- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have installed s10 GX dev kit fpga card on Ubuntu 18.04 and program the Avalon MM+ Hard IP to the card.

While I meet some issues when testing the DMA feature.

For the test application which locates at ~/avmm_bridge_512_0_example_design/software/user/example/intel_fpga_pcie_link_test, all the test mode cannot run successfully.

For example, the first test, Doing 100 writes and 100 reads, failed. I put the results of first 10 tries below.

At dword 0x0

Wrote 0x120aed54

Read 0xffffffff

At dword 0x1

Wrote 0x4db4d210

Read 0xffffffff

At dword 0x2

Wrote 0x616cd2bb

Read 0xffffffff

At dword 0x3

Wrote 0x29ad0aff

Read 0xffffffff

At dword 0x4

Wrote 0x31f54bf7

Read 0xffffffff

At dword 0x5

Wrote 0x7f08785d

Read 0xffffffff

At dword 0x6

Wrote 0x4fde1236

Read 0xffffffff

At dword 0x7

Wrote 0x401d6525

Read 0xffffffff

At dword 0x8

Wrote 0x44a0f03b

Read 0xffffffff

At dword 0x9

Wrote 0x49ebcbdc

Read 0xffffffffFor each time testing, the result of reading from the memory is 0xffffffff. While it shows reading and writing operaions don't meet errors. Only the numbers don't match.

Number of write errors: 0

Number of read errors: 0

Number of dword mismatches: 100While I look into the code, I do not find where the device memory address is initialized for device memory. It is just initialized to NULL.

char *addr = NULL;I am wondering why the test application does not use memory map to get a address mapping to the FPGA card memory. I'm not sure if it is initialized in other functions and whether the address(NULL) is the reason to cause the mismatches.

However, other testing mode cannot work as well. So maybe there are caused by other reasons.

When I installed the PCIe driver for the FPGA card, as the provided driver code is for CentOS, I modified some code to make it could be successfully installed on Ubuntu. Not sure if my modifications will cause any issue.

Hope someone have ideas on the issues I've met. Thank you and look forward to reply.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The problem you seen might related to below KBD

Why does the Intel® Stratix® 10 Avalon®-MM Interface for PCIe* with DMA example design fail the link test and the DMA test when using the default selected BAR0?

When the internal DMA Descriptor Controller is enabled, the BAR0 Avalon®-MM master is not available for general-purpose usage. The DMA Descriptor Controller uses this BAR0 interface through which the host CPU programs in the descriptor table.

The intel_fpga_pcie_link_test user application selects BAR0 as default when it's initially executed. If the user forgets to change to BAR2, which is where the onchip memory is attached, then both the link test and the DMA test will fail.

The user must change to BAR2 before executing the link test and the DMA test.

See the execution transcript of the intel_fpga_pcie_link_test user application below for how to change to BAR2.

~$ sudo ./intel_fpga_pcie_link_test

*********************************************************

Intel FPGA PCIe Link Test

Version 2.0

0: Automatically select a device

1: Manually select a device

*********************************************************

> 0

Opened a handle to BAR 0 of a device with BDF 0x1300

*********************************************************

0: Link test - 100 writes and reads

1: Write memory space

2: Read memory space

3: Write configuration space

4: Read configuration space

5: Change BAR

6: Change device

7: Enable SRIOV

8: Do a link test for every enabled virtual function

belonging to the current device

9: Perform DMA

10: Quit program

*********************************************************

> 5

Changing BAR...

Enter BAR number (-1 for none):

> 2

Successfully changed BAR!

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

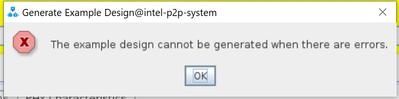

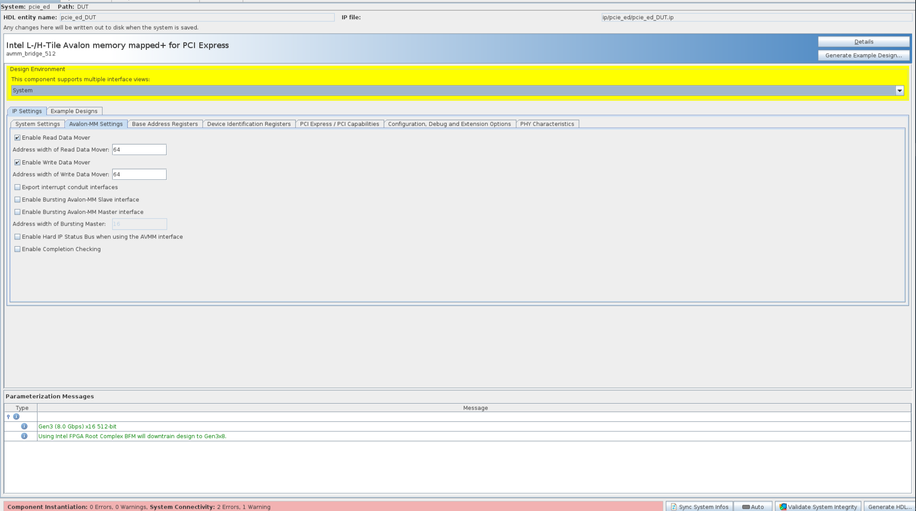

When I de-select the "Enable Bursting Avalon-MM Master interface", it shows there are 2 errors of system connectivity(at the bottom of the 2nd pic), and I cannot generate the design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

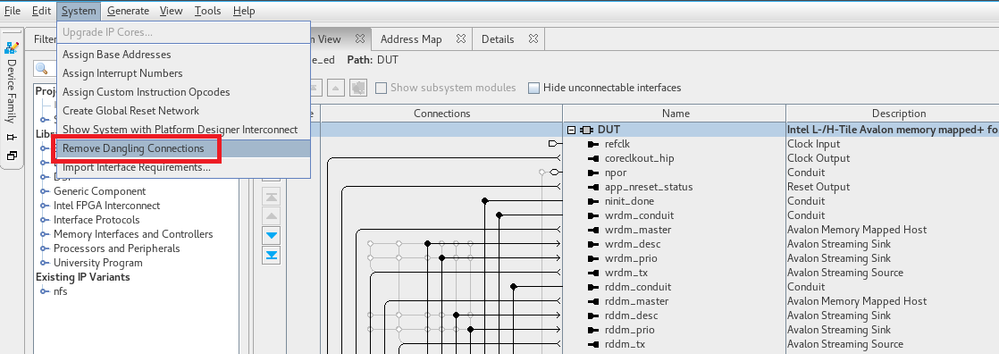

On 'System' tab, click 'Remove Dangling Connections'

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

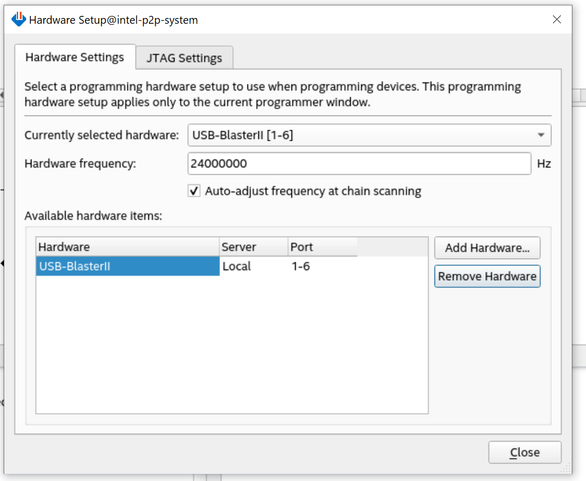

I just notice another setting. The Avalon MM need to operate at 250MHz, right? Do I need to change the hardware frequency to 250MHz when I am programming the design to card?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The screenshot you shared here is the JTAG clock frequency of the USB-Blaster II download cable. The JTAG TCK or DCLK frequency can be either 24M, 16M and 6M.

I don't think it has relationship with the PCIe IP Avalon-MM setting.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Unfortunately, the same error still occurs.

This time DMA test runs a bit longer than before. The usb is disconnected after 20,000 loops of testing.

At the same time, during the test, I found that the previous usb was connected to an usb3.0 interface of the motherboard, so I plugged it into an usb2.0. While no difference about the result.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Atfer how much time the USB will be disconnected seems very random. Maybe I just start the test, or have runned the test for a while.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think it is very likely that the temperature is too high to make the USB disconnected. I notice in user guide documentation https://www.intel.com/content/www/us/en/docs/programmable/683674/current/thermal-limitations-and-protection.html , it mentions that the board will be powered off when the temperature crosses 100C. Then we need to replug the power supply to make it work again. It's very similar to our situation. I have added a tiny fan blowing the card directly to see whether it could work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good to know that the USB connection issue could be potentially caused by high temperature.

Make sense that since the DMA test can perform up to 20k cycles, doesn't seems like it is design issue anymore.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yep. And thank you very much for your support and patience.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »