- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

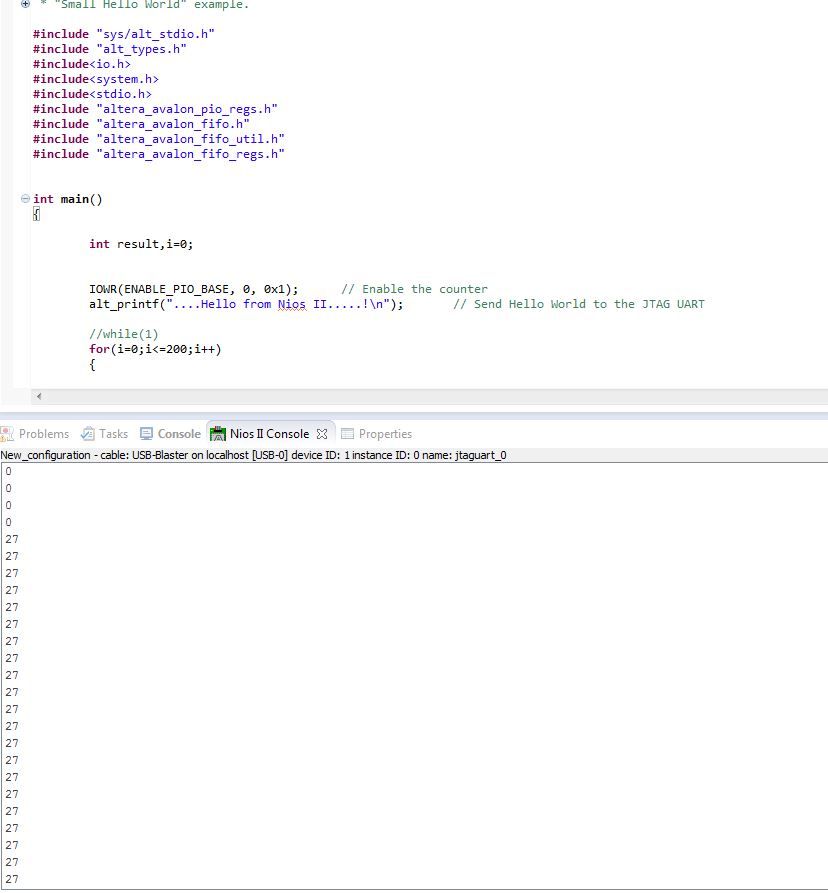

I would like to have some advice to write the c code in NIOS. The counter must sends bits continuously to FIFO but the counter must stops when the FIFO is almost full. When the FIFO returns almost_empty the counter must restarts.

I have pasted FIFO files. Thanks in advance.

HEADER FILE

#ifndef __ALTERA_AVALON_FIFO_REGS_H__

#define __ALTERA_AVALON_FIFO_REGS_H__

#include <io.h>

#define ALTERA_AVALON_FIFO_OTHER_INFO_REG 1

#define ALTERA_AVALON_FIFO_DATA_REG 0

#define ALTERA_AVALON_FIFO_LEVEL_REG 0

#define ALTERA_AVALON_FIFO_STATUS_REG 1

#define ALTERA_AVALON_FIFO_EVENT_REG 2

#define ALTERA_AVALON_FIFO_IENABLE_REG 3

#define ALTERA_AVALON_FIFO_ALMOSTFULL_REG 4

#define ALTERA_AVALON_FIFO_ALMOSTEMPTY_REG 5

// Read slave

#define IORD_ALTERA_AVALON_FIFO_DATA(base) \

IORD(base, ALTERA_AVALON_FIFO_DATA_REG)

#define IORD_ALTERA_AVALON_FIFO_OTHER_INFO(base) \

IORD(base, ALTERA_AVALON_FIFO_OTHER_INFO_REG)

// Write slave

#define IOWR_ALTERA_AVALON_FIFO_DATA(base, data) \

IOWR(base, ALTERA_AVALON_FIFO_DATA_REG, data)

#define IOWR_ALTERA_AVALON_FIFO_OTHER_INFO(base, data) \

IOWR(base, ALTERA_AVALON_FIFO_OTHER_INFO_REG, data)

// Control slave

#define IORD_ALTERA_AVALON_FIFO_LEVEL(base) \

IORD(base, ALTERA_AVALON_FIFO_LEVEL_REG)

#define IORD_ALTERA_AVALON_FIFO_STATUS(base) \

IORD(base, ALTERA_AVALON_FIFO_STATUS_REG)

#define IORD_ALTERA_AVALON_FIFO_EVENT(base) \

IORD(base, ALTERA_AVALON_FIFO_EVENT_REG)

#define IORD_ALTERA_AVALON_FIFO_IENABLE(base) \

IORD(base, ALTERA_AVALON_FIFO_IENABLE_REG)

#define IORD_ALTERA_AVALON_FIFO_ALMOSTFULL(base) \

IORD(base, ALTERA_AVALON_FIFO_ALMOSTFULL_REG)

#define IORD_ALTERA_AVALON_FIFO_ALMOSTEMPTY(base) \

IORD(base, ALTERA_AVALON_FIFO_ALMOSTEMPTY_REG)

#define IOWR_ALTERA_AVALON_FIFO_EVENT(base, data) \

IOWR(base, ALTERA_AVALON_FIFO_EVENT_REG, data)

#define IOWR_ALTERA_AVALON_FIFO_IENABLE(base, data) \

IOWR(base, ALTERA_AVALON_FIFO_IENABLE_REG, data)

#define IOWR_ALTERA_AVALON_FIFO_ALMOSTFULL(base, data) \

IOWR(base, ALTERA_AVALON_FIFO_ALMOSTFULL_REG, data)

#define IOWR_ALTERA_AVALON_FIFO_ALMOSTEMPTY(base, data) \

IOWR(base, ALTERA_AVALON_FIFO_ALMOSTEMPTY_REG, data)

#define ALTERA_AVALON_FIFO_EVENT_F_MSK (0x01)

#define ALTERA_AVALON_FIFO_EVENT_E_MSK (0x02)

#define ALTERA_AVALON_FIFO_EVENT_AF_MSK (0x04)

#define ALTERA_AVALON_FIFO_EVENT_AE_MSK (0x08)

#define ALTERA_AVALON_FIFO_EVENT_OVF_MSK (0x10)

#define ALTERA_AVALON_FIFO_EVENT_UDF_MSK (0x20)

#define ALTERA_AVALON_FIFO_EVENT_ALL (0x3F)

#define ALTERA_AVALON_FIFO_STATUS_F_MSK (0x01)

#define ALTERA_AVALON_FIFO_STATUS_E_MSK (0x02)

#define ALTERA_AVALON_FIFO_STATUS_AF_MSK (0x04)

#define ALTERA_AVALON_FIFO_STATUS_AE_MSK (0x08)

#define ALTERA_AVALON_FIFO_STATUS_OVF_MSK (0x10)

#define ALTERA_AVALON_FIFO_STATUS_UDF_MSK (0x20)

#define ALTERA_AVALON_FIFO_STATUS_ALL (0x3F)

#define ALTERA_AVALON_FIFO_IENABLE_F_MSK (0x01)

#define ALTERA_AVALON_FIFO_IENABLE_E_MSK (0x02)

#define ALTERA_AVALON_FIFO_IENABLE_AF_MSK (0x04)

#define ALTERA_AVALON_FIFO_IENABLE_AE_MSK (0x08)

#define ALTERA_AVALON_FIFO_IENABLE_OVF_MSK (0x10)

#define ALTERA_AVALON_FIFO_IENABLE_UDF_MSK (0x20)

#define ALTERA_AVALON_FIFO_IENABLE_ALL (0x3F)

#endif /* __ALTERA_AVALON_FIFO_REGS_H__ */#define ALT_MODULE_CLASS_fifo_0_in_csr altera_avalon_fifo

#define FIFO_0_IN_CSR_AVALONMM_AVALONMM_DATA_WIDTH 32

#define FIFO_0_IN_CSR_AVALONMM_AVALONST_DATA_WIDTH 32

#define FIFO_0_IN_CSR_BASE 0x11000

#define FIFO_0_IN_CSR_BITS_PER_SYMBOL 16

#define FIFO_0_IN_CSR_CHANNEL_WIDTH 8

#define FIFO_0_IN_CSR_ERROR_WIDTH 8

#define FIFO_0_IN_CSR_FIFO_DEPTH 4096

#define FIFO_0_IN_CSR_IRQ 1

#define FIFO_0_IN_CSR_IRQ_INTERRUPT_CONTROLLER_ID 0

#define FIFO_0_IN_CSR_NAME "/dev/fifo_0_in_csr"

#define FIFO_0_IN_CSR_SINGLE_CLOCK_MODE 1

#define FIFO_0_IN_CSR_SPAN 32

#define FIFO_0_IN_CSR_SYMBOLS_PER_BEAT 2

#define FIFO_0_IN_CSR_TYPE "altera_avalon_fifo"

#define FIFO_0_IN_CSR_USE_AVALONMM_READ_SLAVE 1

#define FIFO_0_IN_CSR_USE_AVALONMM_WRITE_SLAVE 1

#define FIFO_0_IN_CSR_USE_AVALONST_SINK 0

#define FIFO_0_IN_CSR_USE_AVALONST_SOURCE 0

#define FIFO_0_IN_CSR_USE_BACKPRESSURE 1

#define FIFO_0_IN_CSR_USE_IRQ 1

#define FIFO_0_IN_CSR_USE_PACKET 1

#define FIFO_0_IN_CSR_USE_READ_CONTROL 0

#define FIFO_0_IN_CSR_USE_REGISTER 0

#define FIFO_0_IN_CSR_USE_WRITE_CONTROL 1

/*

* fifo_0_out configuration

*

*/

#define ALT_MODULE_CLASS_fifo_0_out altera_avalon_fifo

#define FIFO_0_OUT_AVALONMM_AVALONMM_DATA_WIDTH 32

#define FIFO_0_OUT_AVALONMM_AVALONST_DATA_WIDTH 32

#define FIFO_0_OUT_BASE 0x11050

#define FIFO_0_OUT_BITS_PER_SYMBOL 16

#define FIFO_0_OUT_CHANNEL_WIDTH 8

#define FIFO_0_OUT_ERROR_WIDTH 8

#define FIFO_0_OUT_FIFO_DEPTH 4096

#define FIFO_0_OUT_IRQ -1

#define FIFO_0_OUT_IRQ_INTERRUPT_CONTROLLER_ID -1

#define FIFO_0_OUT_NAME "/dev/fifo_0_out"

#define FIFO_0_OUT_SINGLE_CLOCK_MODE 1

#define FIFO_0_OUT_SPAN 4

#define FIFO_0_OUT_SYMBOLS_PER_BEAT 2

#define FIFO_0_OUT_TYPE "altera_avalon_fifo"

#define FIFO_0_OUT_USE_AVALONMM_READ_SLAVE 1

#define FIFO_0_OUT_USE_AVALONMM_WRITE_SLAVE 1

#define FIFO_0_OUT_USE_AVALONST_SINK 0

#define FIFO_0_OUT_USE_AVALONST_SOURCE 0

#define FIFO_0_OUT_USE_BACKPRESSURE 1

#define FIFO_0_OUT_USE_IRQ 1

#define FIFO_0_OUT_USE_PACKET 1

#define FIFO_0_OUT_USE_READ_CONTROL 0

#define FIFO_0_OUT_USE_REGISTER 0

#define FIFO_0_OUT_USE_WRITE_CONTROL 1#ifndef __ALT_FIFO_UTIL_H__

#define __ALT_FIFO_UTIL_H__

#ifdef __cplusplus

extern "C"

{

#endif /* __cplusplus */

#include "altera_avalon_fifo_regs.h"

#define ALTERA_AVALON_FIFO_TYPE (volatile alt_u32*)

int altera_avalon_fifo_init(alt_u32 address, alt_u32 ienable,

alt_u32 emptymark, alt_u32 fullmark);

int altera_avalon_fifo_read_status(alt_u32 address, alt_u32 mask);

int altera_avalon_fifo_read_ienable(alt_u32 address, alt_u32 mask);

int altera_avalon_fifo_read_almostfull(alt_u32 address);

int altera_avalon_fifo_read_almostempty(alt_u32 address);

int altera_avalon_fifo_read_event(alt_u32 address, alt_u32 mask);

int altera_avalon_fifo_read_level(alt_u32 address);

int altera_avalon_fifo_clear_event(alt_u32 address, alt_u32 mask);

int altera_avalon_fifo_write_ienable(alt_u32 address, alt_u32 mask);

int altera_avalon_fifo_write_almostfull(alt_u32 address, alt_u32 data);

int altera_avalon_fifo_write_almostempty(alt_u32 address, alt_u32 data);

int altera_avalon_fifo_write_fifo(alt_u32 write_address, alt_u32 ctrl_address,

alt_u32 data);

int altera_avalon_fifo_write_other_info(alt_u32 write_address, alt_u32 ctrl_address,

alt_u32 data);

int altera_avalon_read_fifo(alt_u32 read_address, alt_u32 ctrl_address, int *data);

int altera_avalon_fifo_read_fifo(alt_u32 read_address, alt_u32 ctrl_address);

int altera_avalon_fifo_read_other_info(alt_u32 read_address);

int altera_avalon_fifo_read_backpressure (alt_u32 read_address);

//Return Codes

#define ALTERA_AVALON_FIFO_OK 0

#define ALTERA_AVALON_FIFO_EVENT_CLEAR_ERROR -1

#define ALTERA_AVALON_FIFO_IENABLE_WRITE_ERROR -2

#define ALTERA_AVALON_FIFO_THRESHOLD_WRITE_ERROR -3

#define ALTERA_AVALON_FIFO_FULL -4

#ifdef __cplusplus

}

#endif /* __cplusplus */

#endif /* __ALT_FIFO_UTIL_H__ */

Link Copied

2 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I saw one of your post requesting the same https://forums.intel.com/s/question/0D50P000042Emtf/fifohow-to-slow-down-the-clock-frequency-from-50-mhz?s1oid=00DU0000000YT3c&OpenCommentForEdit=1&s1nid=0DB0P000000U1Hq&emkind=chatterCommentNotification&s1uid=0050P000008IfWN&emtm=1537339138426&fromEmail=1&s1ext=0, Am I correct?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, you are right. I am unable to complete this task. Please guide me.

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page