- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone!

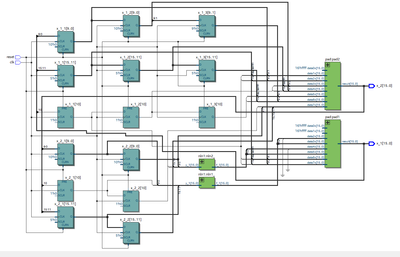

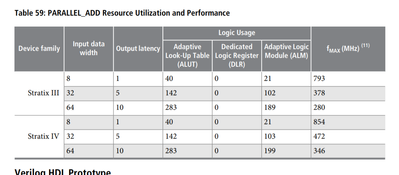

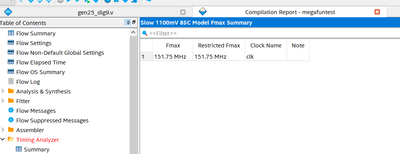

I don't know am I asking question at right place, I need help with optimizing my FPGA project in terms of freqs. I am trying to generate chaotic signal on FPGA board, chaotic oscillator described as IIR filter with nonlinear module (fig. 1), to realize that I used parallel add module from basic functions catalog. I found information about parallel add module only for Stratix devices (fig.2) On my Cyclone® V SE 5CSEMA4U23C6N device I get about 150 MHz FMax (fig. 3) and without non linear module about 200 MHz, am I doing something wrong or Cyclone V is slower than old Stratix devices? Can you give me advice how can I get higher FMax for this project?

And sorry for my poor English.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry for the late reply as I was in vacation,

1. It really depends on how fast you want to run on the particular path. Let say your register to register is running at 200Mhz, and you want that path to run faster, then set max delay is a option to do that. If you want to stick with 200Mhz, just let the Quartus do the job and see if the timing closed? If it is not close, you can try overconstrain or add more pipeline towards the path.

2. Yes, you are right. But if you are using older devices, most likely you will not need this as is for S10 and above hyperflex timing closure. Older device we just monitor the max fan out.

3. It is compulsory to meet both of the model, whether it is fast or slow. You may take a look in https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/wp/wp-01139-timing-model.pdf, and https://www.youtube.com/watch?v=6D-w8mOttnE at time 26:33

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What does your .sdc file look like?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I hoped that project is small and Quartus will anyway compile it fastest possible way, so I didn't make time constraints, do I need to do it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can time constraints change freqs from 200 MHz up to 470 MHz like for Stratix devices?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Absolutely. You should have a .sdc file for every design, especially if you're trying to achieve those types of speeds.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank You for your response! I will try to understand the timing analyzer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear sstrell

On your advice, I began to study timing analysis and I had several questions.

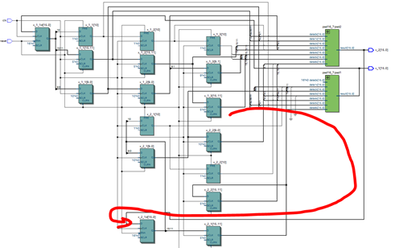

1. Do I understand correctly that setting the minimum and maximum delay constraints is necessary only for asynchronous combinatorial logic? Whether it is necessary to set, apart from the clocks constraints, the delay constraints for the synchronous register-comb logic-register case (fig 1), like set_max_delay -from [get_registers {x_1_3*}] -to [get_registers x_2_1d*] X ns?

2. Also, while reading the literature (https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qpp-timing-analyzer.pdf, page 44), I learned that a large number of outputs from one register can also limit the maximum frequency of the circuit. But I did not find the Design metrics in the timing analyzer in Quartus Light to automatically fix this problem, do I need to purchase the pro version for this?

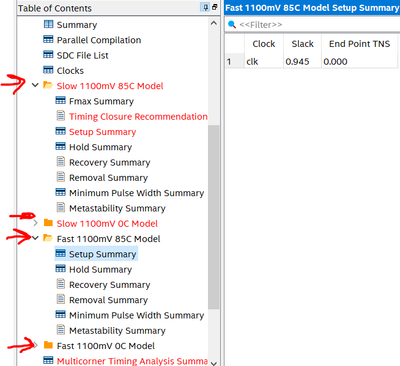

3. Another question concerns fast and slow models in Quartus. If the time constraints are met for the fast model, but not for the slow model (fig 2), what should I do to make the crystal work in the fast mode?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You may also take a look the video

On how to apply constrain

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can somebody else help me with my questions above?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry for the late reply as I was in vacation,

1. It really depends on how fast you want to run on the particular path. Let say your register to register is running at 200Mhz, and you want that path to run faster, then set max delay is a option to do that. If you want to stick with 200Mhz, just let the Quartus do the job and see if the timing closed? If it is not close, you can try overconstrain or add more pipeline towards the path.

2. Yes, you are right. But if you are using older devices, most likely you will not need this as is for S10 and above hyperflex timing closure. Older device we just monitor the max fan out.

3. It is compulsory to meet both of the model, whether it is fast or slow. You may take a look in https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/wp/wp-01139-timing-model.pdf, and https://www.youtube.com/watch?v=6D-w8mOttnE at time 26:33

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for reply!

3. Timing analysis shows huge difference between fast and slow models. Whereas fast model reaches up to 330 MHz FMax, slow model reaches only about 200 MHz for same Cyclone V 5CSEMA4U23C6N chip. Therefore, I was wandering how could I provide the chip with required conditions to gain fast model frequencies.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How do you check on this? Usually, it should not be that huge different.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

any update?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We do not receive any response from you to the previous reply that we have provided. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page