- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have designed a system which uses a Max 10 (10M08SCU169I7G) with a Micron flash (MT28EW128ABA1HPN) connected to it, to configure a Cyclone 10 LP (10CL040YF484I7G) in Passive Serial mode.

I am using separate loads for the Max 10. One to program the flash and one to configure the Cyclone 10 LP. Therefore the program load has the Parallel Flash Loader set for Program only and the Configure load has the Parallel Flash Loader set for Configure only.

The Quartus tool "Convert Programming File" is set as follows:

Programming file type: Programmer Object File (.pof)

Options/Boot info: Option bit address 0xFFE000, enhanced compression not enabled.

Configuration device: CFI_128Mb

Mode: 1-bit Passive Serial

Advanced: default values

Input files to convert: Using .sof file created for Cyclone 10 LP, no compression.

The Max 10 is first loaded with the Program load (.pof). The Micron flash is recognized after scanning and is then program with the file (.pof) created by the "Convert Programming File" tool.

The Max 10 is then loaded with the Configure load (.pof) for which the PFL FPGA configuration is as follows:

External Clk: 48.0 MHz

Flash access time: 90 ns

Byte address of option bits: 0x00FFE000

Configuration scheme: Passive Serial

Configuration failure: Retry same page

Byte address to retry from on failure: 0x00000000

Ration input clk and DCLK: 2

Use advance read mode: 32 Bytes Page Mode (MT28EW)

Enable enhanced bitstream-decompression block: none

Simulation shows the configuration starts properly. The options bits are read correctly (version 03, start addr and end addr as per .map file created by "Convert Programming File" tool.), and the DCLK and Data start sometime afterwards with the data corresponding to the .pof file values starting after some header, with LSB first.

The problem is that the Cyclone 10 LP never set the Config_Done line high and the Max 10 continuously tries to program it as seen by the Status_n and Config_n lines pulsing low. Various changes in the PFL settings didn't fix the problem.

To get more info on the issue, the Cyclone 10LP was programmed directly via JTAG with the original .sof file and it programmed successfully. The Config_Done line was probed and was now high. Further the Max 10 stopped trying to program the Cyclone 10 LP, recognizing the high on the Config_Done line.

So the question is : Why can't the Max 10 configure the Cyclone 10 LP in Passive Serial mode?

- Tags:

- Programmable Devices

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mike,

May I know do you use Intel Cyclone LP dev kit or your custom Board?

I suspect it might happen due to HW on board since Status_n and Config_n always pulse to low.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using a custom board. The reason the Status_n and Config_n always pulse low is because I have chosen such an option for the Parallel Flash Loader Configuration load:

Configuration failure: Retry same page

If the Configuration failure option is set to "Halt on error" there is no pulsing low of the Status_n and Config_n as there is no retry in this case. Note that for the first configuration attempt, the Config_n and Status_n do not pulse low before configuration starts, as per the Intel PGL User Guide document. This is consistent with the signal waveforms I am getting from the SignaTap analyser of the Max 10.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mikel,

Here some option you can try:

- In MAX 10 design, Ensure that the unused pins are reserved as input tri-stated. Go to Assignment → Device → Device & pin options → Unused Pins.

- Is your design use ratio input clk to Dclk =2? if not, maybe you can change it to 1.

- For "Use advance read mode: " option, can you change it to "normal" instead of "32 Bytes Page Mode (MT28EW)"?

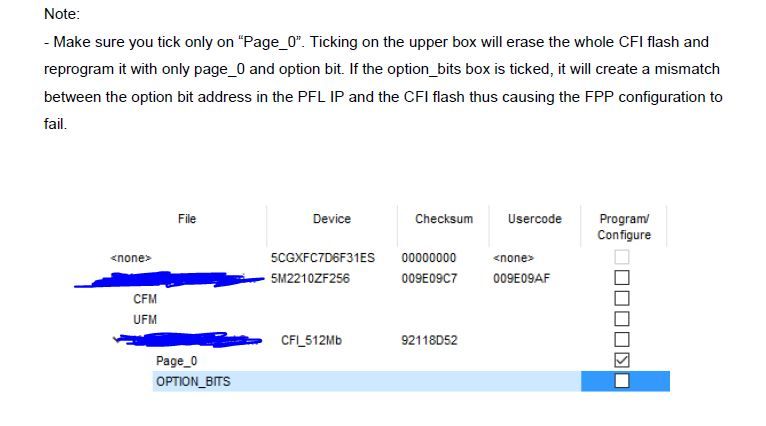

- when you want to program the design into CFI flash, Make sure you tick only on "your design". do not tick the bit_option. refer image below for more details:

If your issue have not improve, please let me know.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wolfgang,

- I didn't list that setting in my original description, however this option is set for "input tri-stated with weak pullup".

- The DCLK ratio is set to 2. A ratio of 1 doesn't work.

- I already tried to change the Advance Read Mode to normal without success.

- I had both the Page and Option Bits checked. Programming the flash without the Option Bits works.

I would suggest that this particular bit of information for programming the flash be included in the PFL user guide.

Thanks for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mikel,

I am glad to hear that your issue is resolved.

Cheers

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page