- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We have an issue of qsys component, but have no idea to debug further.

In our design, there is a Qsys component auto-generated by Quartus,

it transforms Avalon-MM interface to AXI4 interface.

According to SignalTap waveform, the component get a read request, but waitrequest signal is always high.

And it never send the request to the next AXI bridge.

Do you have any suggestion?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chiaming,

Is there any possible screenshots or files that you could provide to get better understanding?

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes,

the attached image is signalTap waveform.

It shows that hbm2_ccb bridge send a read request,

but stuck at the request.

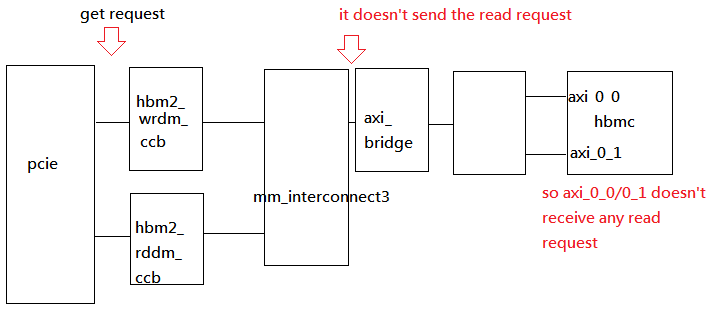

The following figure shows block diagram. (Actually it's AN881 reference design for S10 MX FPGA dev. kit.)

According to attached signalTap waveform,

CCB send the read request to mm_interconnect_3 which is Qsys component.

Then mm_interconnect_3 doesn't send the request to axi_bridge.

We think there must be something wrong inside mm_interconnect.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm experiencing similar issue.

I have AXI master with burst capabilities, which connects to PCIe txs slave.

I got issues with QSYS interconnect so I removed any CDC and width change so that QSYS will only do AXI to Avalon adapter.

I see issue that after first read, write, I get the fabric stuck, because the ARvalid coming from my master is not passing the interconnect towards the PCIe- in signal tap I see that read_i is never asserted.

Please assist! This is an example of Intel design and IP cores that is NOT FUNCTIONAL.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page