- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am using Stratix 10 SX Development Kit and I want to control UART1 output something by using HPS. How many and what kind of registers should I configure like l4_sp register for Cyclone V device in u-boot.scr file to achieve my goal?

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can anyone help me?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi stanley015,

Have you enabled the HPS UART 1 in your qsys in Platform designer?

Then consider the changes to add UART1 in the device tree when building your U-boot. By default, UART0 is already enabled and it's default settings can be seen in the device tree configuration for reference.

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello aikeu,

Thanks for replying!

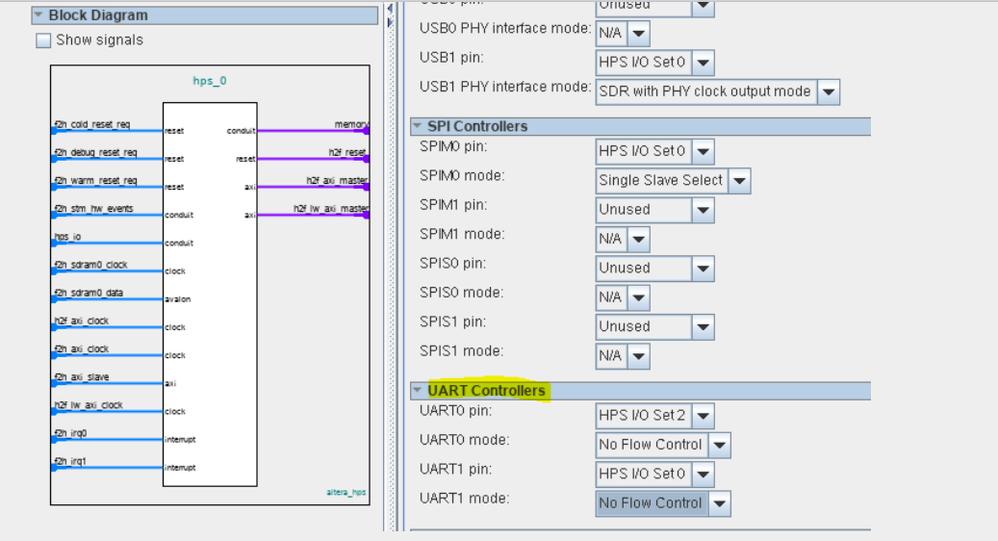

Firstly, I am pretty sure I enable the HPS UART 1 in your qsys in Platform designer.

Then I am trying to use U-Boot as the Secure Monitor (non-ATF way) to control UART1 on L4 Slave Peripheral BusI, so the way I do is to use the pre-built sdimage downloaded online, which contains four files in FAT32 such as "Image", "u-boot-dtb.img", "u-boot.scr", "socfpga_stratix10_socdk.dtb". I keep "Image" and "u-boot-dtb.img" the same as before. I change "u-boot.scr" with adding l4_sp register (mw.l 0xFFD21070 0x01010101) configuration to enable both secure and non-secure transactions for all masters (axi_ap, F2H, mpu, dma) to UART1. Also I update "socfpga_stratix10_socdk.dtb" with UART1's status changing from "disable" to "okay".

However, what I have done does not make UART1 output something which the output data is always in loop of UART1 register (0xFFC02114).

Could you please give me some advice about my situation?

Thanks.

Regards,

Stanley

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi stanley015,

For "Image", "u-boot-dtb.img", "u-boot.scr", "socfpga_stratix10_socdk.dtb",

I think u-boot-dtb.img will requires compilation changes as well.

Can try adding these two items in your socfpga_stratix10_defconfig:

CONFIG_SPECIFY_CONSOLE_INDEX=y

CONFIG_CONS_INDEX=2

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello aikeu,

I am sorry I forget to renew my comment. I try to add those two items in my socfpga_stratix10_defconfig but it still does not work.

However, I have something new which I open another community https://community.intel.com/t5/FPGA-SoC-And-CPLD-Boards-And/How-to-Read-Write-L4-Peripheral-Slave-Bus-on-S10-SX-Device/td-p/1364632.

This new community shows more information about my problem. Could you please check this new community and if you have any suggestions please let me know.

Best Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hans_1st,

I do not have further suggestion after I go through the details on other thread.

I think the direction provided in the other thread is correct to what you are working on.

I will comment in the other thread if there is any further info which I can provide.

I will close this thread for now.

Thanks.

Regards,

Aik Eu

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page