- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am having a question on HPS side memory controller.

The timing analyzer complain the timing issue of HPS memory DQS signals.

But from the message I received, all the HPS peripherals like USB, I2C clocks and memory controller need not doing any timing constraint as they are hard coded.

And Quartus will handle it automatically.

Is it correct?

I don't care any timing complaints on HPS side.

Please let me know.

Thank you!

BRs,

Johnson

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

Firstly, may I know which Quartus version and SoC device are you currently working on?

Is it possible for you to share the message that you are seeing or screenshot? Which ever is easy for you, so that I can check what type of message is to be ignored.

Yes, timing constraints are fixed for both dedicated HPS I/Os for Cyclone V SoC and Arria 10 SoC you do not need to define it.

You may refer below for more information regarding the timing constraints on our SoC devices (refer Table 7 on both links )

Cyclone V SoC:

https://www.intel.com/content/www/us/en/programmable/documentation/doq1481305867183.html#qpb1481303809420

Arria 10 SoC:

https://www.intel.com/content/www/us/en/programmable/documentation/pde1458159073865.html#pde1458163562367

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thank you for getting back!

I am using Quartus 16.0.2 and the device is 5CSXFC2C6U23C8.

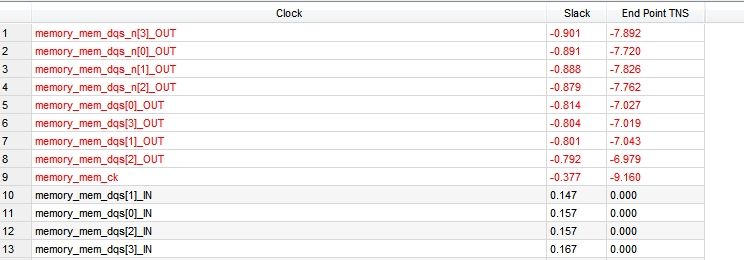

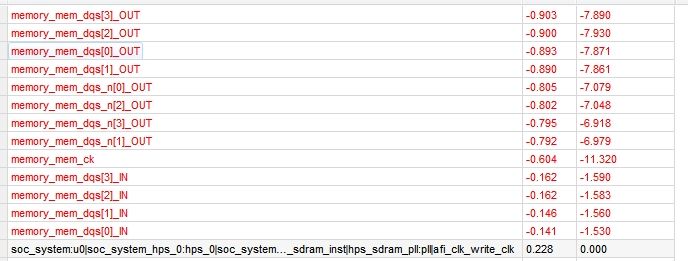

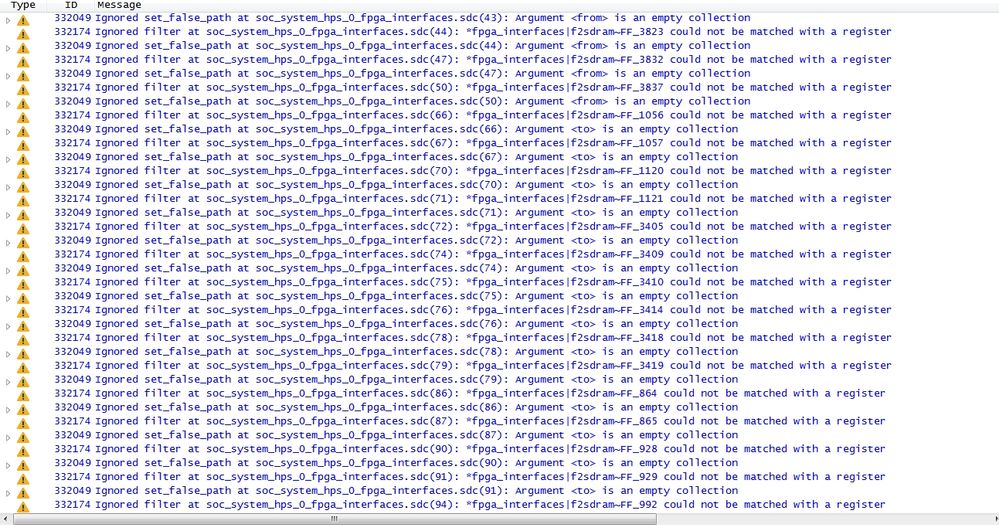

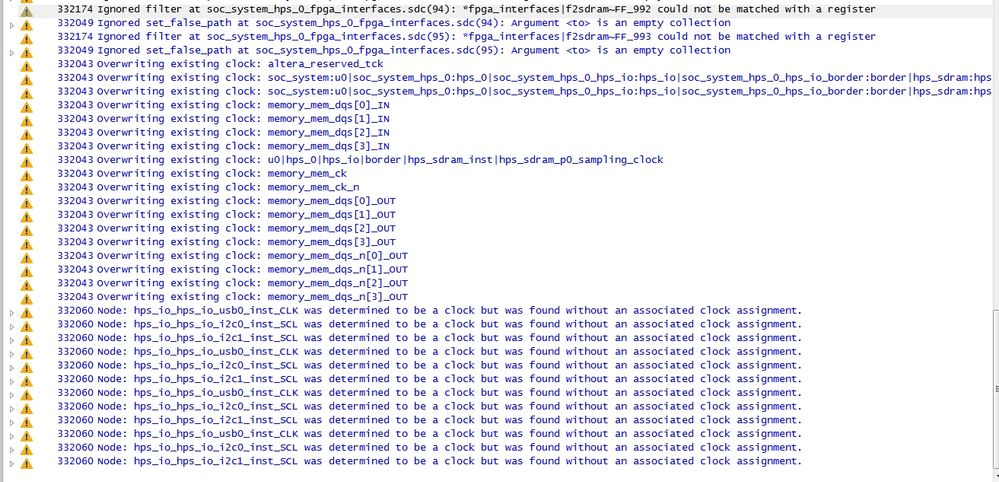

Below are Setup and hold time violation message.

Thank you!

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

I believe the screenshot are the timing compilation report.

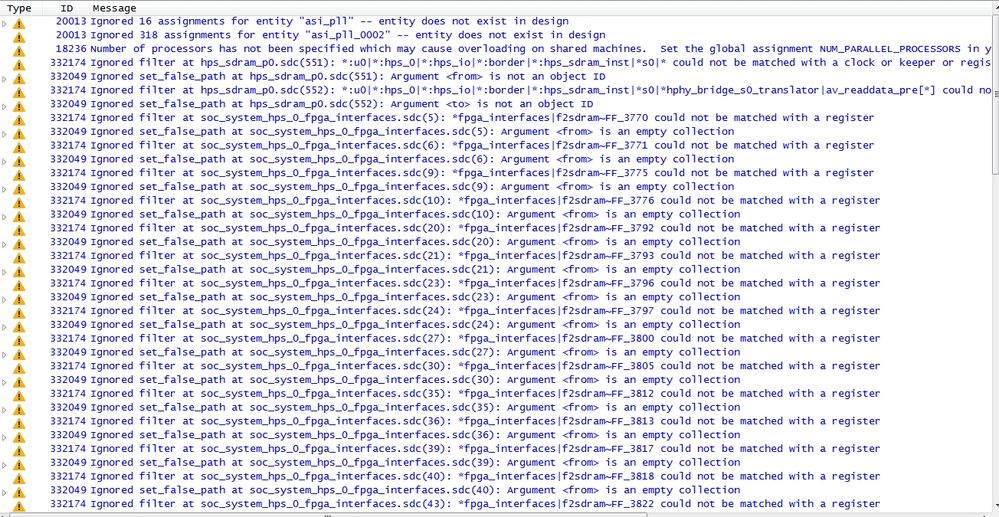

Warnings report can be seen at the bottom of the screen, e.g:

Warning (332174): .....

Warning (332174): ....

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi EL,

Thank you for the correction.

Attached are warning report,

FYI!

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

Thanks.

Yes, as you mentioned these timing analyzer warnings can be ignored.

Best Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi EL,

Thanks for the answer and support!

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

Glad to help, I hope I have answered your question.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page