- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I got some problems when using RSU in Cycone IV E device:

1: When using RSU, is it necessary to use an external trigger to trigger the FPGA to load the application image? I try to use logic to trig reconfiguration after power on, if no error accurs, appliaction is load successfully,and when some contents of application image are erased, FPGA is thought to fall back to factory image ,but i found my FPGA will contiously reconfiguring.

2: Why can't I get the reason for reconfiguration by reading the register when the application image fails to load and returns to the factory image? I want to get the reason for the last FPGA reconfiguration, and based on this reason to determine whether to start loading the application image, this should avoid the FPGA into the loop reconfiguration, but never get this information through the read register.

3: The same loading process, why use the avalon-mm interface in the factory image I can not trigger the FPGA to load the application image, but the non-avalon-mm interface trig successfully?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The pof_error only performed sanity check and not full check. So if the initial bitstream is correct then it will try to configure the FPGA with application image. The pof_error will only detect if there is some error on the initial bitstream.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

1: When using RSU, is it necessary to use an external trigger to trigger the FPGA to load the application image? I try to use logic to trig reconfiguration after power on, if no error accurs, appliaction is load successfully,and when some contents of application image are erased, FPGA is thought to fall back to factory image ,but i found my FPGA will contiously reconfiguring.

No. Internal trigger is also fine. Do you enable "Enable reconfig POF checking"? If not, could you enabled this features?

2: Why can't I get the reason for reconfiguration by reading the register when the application image fails to load and returns to the factory image? I want to get the reason for the last FPGA reconfiguration, and based on this reason to determine whether to start loading the application image, this should avoid the FPGA into the loop reconfiguration, but never get this information through the read register.

You can avoid it by enabling "Enable reconfig POF checking" in Remote Upgrade IP.

3: The same loading process, why use the avalon-mm interface in the factory image I can not trigger the FPGA to load the application image, but the non-avalon-mm interface trig successfully?

May I know how do you performed it in avalon-mm interface?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,JohnT

Thanks for your reply.

1,2:I didn't enable "Enable reconfig POF checking",so i try to enable it after recieving your reply,but i still can not get the reason for last reconfiguration by reading regisiters and all combinations of read_source had been tested, so i use pof_error to trig reconfiguration, when application image is erased,the machine fallback sucessfully,but once been writen partitally, it still reconfig contiously,how does RSU check POF,does it only check wether there is data in image but not the CRC?

3:Load process in avalon_mm interface: reset -- set cd_early -- read reconfig_source -- set osc_int -- set wd_value -- enable watchdog -- set reconfig address --reconfig

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know how do you write it partially, The POF checking is checking the initial part of the bitstream to contain the correct bitstream before continuing with reconfiguring the FPGA. May I know if you corrupt only the Application image?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

My application image is consist of 64 sectors,256KB each sector,when the first 10 sectors are writed ,i stop the update process in Host computer,,and FPGA will reconfig contiously after restating.When application image is only erased ,it can fallback successfully,and when all the contents(64sectors) are fully writen, it can update successfully.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Besides,only the Application image is update,factory iamge will never be erased or write in update process.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you share with me your design? The pof_error is used to monitor that there is application image bitstream issue where you should stop reconfiguring your FPGA to application image.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

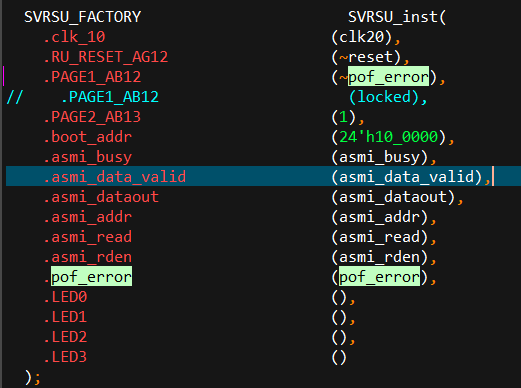

I guess i probally find my problem,the reconfig source.can i use pof_error in this way?My module is as follows.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"PAGE1_AB12" is the reconfig source of RSU,when PAGE1_AB12 goes high, reconfig is started.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

What is PAGE2_AB13? Is it active high for PAGE_AB12 and PAGE_AB13? Is it possible to share SVRSU_Factory module?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If there is no POF_Error then does it mean that it will always try to reconfig the FPGA to Application Image as you tied pof_error to PAGE1_AB12?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

yes,If there is no POF_Error then does it mean that it will always try to reconfig the FPGA to Application Image,and reconifguration only occurs in factory image.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know if it is stuck in the loop that when it load the factory image then it will try to reconfigure to application image? Or is there a way to stop the configuration when it is reverting to factory image after failure?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It can load application image successfully and will not stuck in the loop when both two images are complete,but it will stuck in the loop when application image is corruptted. As far as i am concerned,pof_error is supposed to go high after failure,and it should remain high,so even if it revert to factory image after failure,reconfiguration should not be trigged.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The pof_error check will just performed sanity check and if it confirm that initial data contain valid bitstream then it will try to configure it to application image. If it is failed then it will reload back to factory image. May I know what mechanism or state machine you use to stop it from re-configuring it to application image?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There is nothing to stop it from re-configuring it to application image after reload. so you mean that a high level on pof_error will reload back to factory image,and after reverting to factory image,pof_error will goes low? so if there is no stop,it will stuck in the loop?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The pof_error only performed sanity check and not full check. So if the initial bitstream is correct then it will try to configure the FPGA with application image. The pof_error will only detect if there is some error on the initial bitstream.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,I

Is the initial bitstream stored in the frontmost storage area of image?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

i guess i konw how to avoid the stuck,update the initial bitstream last.could you mind tell my how many bytes does the initial bitstream occupied?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I do not have the information as it is confidential information

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page