- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I am not sure how to describe the problem to be written in the title. So I have a 150mb dataset in .txt, it looks like:

0.123

0.254

0.956

...got like 3 million rows.

I am using the FIFO in sending all data one by one to fpga to perform calculation, it send 20k from HPS to fpga, and on the fpga side it keep on calculating, and once 20k counter is reached, the fpga will output one result to HPS.

Below is the C:

while (j<35)

{

for (k = 0; k<N; k++)

{

fscanf(fp, "%f", &data);

data = fabs(data);

data = data * bin_scale;

scaled_data[k] = (int)data;

}

for (i=0; i<N; i++)

{

FIFO_WRITE_BLOCK(scaled_data[i]);

}

j++;

usleep(1*1000);

}

while(!READ_FIFO_EMPTY)

{

retdata[m] = FIFO_READ;

retdata[m] = retdata[m] / bin_scale;

printf("data %d out %.10f\n",m, retdata[m]);

m++;

}

fclose(fp);and below is the verilog code:

always @(posedge CLOCK_50)

begin

if(initEnable == 0) begin

sram_write <= 1'b0 ;

hex3_hex0[3:0] <= 4'd1;

hex3_hex0[7:4] <= 4'd10;

hex3_hex0[11:8] <= 4'd1;

hex3_hex0[15:12] <= 4'd10;

hex3_hex0[19:16] <= 4'd1;

hex3_hex0[23:20] <= 4'd10;

data_buffer_valid <= 1'b0;

HPS_to_FPGA_state <= 8'd0 ;

FPGA_to_HPS_state <= 8'd0 ;

Processing_state <= 8'd0 ;

initEnable = 1;

end

///////////////////////////////////////////

///////////////////////////////////////////

if ((HPS_to_FPGA_state == 4'd0) && (!(hps_to_fpga_out_csr_readdata[1])))

begin

hps_to_fpga_read <= 1'b1 ; // read data flag

HPS_to_FPGA_state <= 4'd1 ;

end

if (HPS_to_FPGA_state == 4'd1)

begin

hps_to_fpga_read <= 1'b0 ; // zero read data request before data appears

HPS_to_FPGA_state <= 4'd2 ;

end

if ((HPS_to_FPGA_state == 4'd2) && (hps_to_fpga_read == 1'b0))

begin

memo[i] <= hps_to_fpga_readdata ; //read the data to memo[0]

Processing_state <= 4'd5 ; // enter data processing state

HPS_to_FPGA_state <= 4'd3 ;

end

//-----------delay before enter state 0------------//

if (HPS_to_FPGA_state == 4'd3)

begin

HPS_to_FPGA_state <= 4'd4 ;

end

if (HPS_to_FPGA_state == 4'd4)

begin

HPS_to_FPGA_state <= 4'd0 ;

if (i == 125)

begin

i <= 0;

end

else

begin

i <= i+1;

end

end

//////////////////////////////////////////

if (Processing_state == 8'd3)

begin

Processing_state <= 8'd0 ; //return a data packet

end

if ((Processing_state == 4'd5) && (FPGA_to_HPS_state == 0))

begin

a <= a + memo[i] * memo[i];

Processing_state <= 4'd4 ;

end

if (Processing_state == 4)

begin

Processing_state <= 4'd3; //signal fpga the data is ready to be sent

data_buffer_valid <= 1'b1 ;

end

//////////////////////////////////////////

if ((FPGA_to_HPS_state==0) && (!(fpga_to_hps_in_csr_readdata[0])) && data_buffer_valid)

begin

if (|a == 0)

begin

k<=a;

end

else if(|a != 0)

begin

if (j == 20479)

begin

fpga_to_hps_in_writedata <= RMS;

fpga_to_hps_in_write <= 1'b1 ; //write flag

FPGA_to_HPS_state <= 4'd1 ;

end

else

begin

FPGA_to_HPS_state <= 4'd1 ;

end

end

end

if (FPGA_to_HPS_state == 1)

begin

fpga_to_hps_in_write <= 1'b0 ; //data wrote, clear flag

data_buffer_valid <= 1'b0 ; // data sent, clear flag

FPGA_to_HPS_state <= 4'd2 ;

end

//-----------delay before enter state 0------------//

if ((FPGA_to_HPS_state == 2) && (data_buffer_valid == 1'b0))

begin

data_buffer_valid <= 1'b0 ;

FPGA_to_HPS_state <= 4'd0 ;

if (j >= 20479)

begin

j <= 0;

a <= 0;

end

else

begin

j <= j+1;

end

end

////////////////////////////////////////////

////////////////////////////////////////////

end

/////

div #(64, 15, 0, 0) Div (

.a(a),

.b(j+1),

.quotient(mean),

.remainder(),

.divide_by_0()

);

//

sqrt #(64, 0) Sqrt (

.a(mean),

.root(RMS)

);My problem is when the program send back to HPS, it could not send back the 32nd data back to HPS. In the seems like on HPS (C code) side it detect no data in FIFO. If I increase the loop to 50, it will send back 49 data instead of 50, but the data after 32nd data are all messed up. So will the fpga stop after working for certain number of clock pulse?

I am sure the C have no problem.

The verilog have no problem as well I think, because if the verilog have problem, the result would have appear on the first few data send back from fpga, instead it appears on the 32nd.

Also, after the program is ended, and I execute it again, then all the data messed up.

[EDIT]

After re-watching few videos, seems like I found the source problem:

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

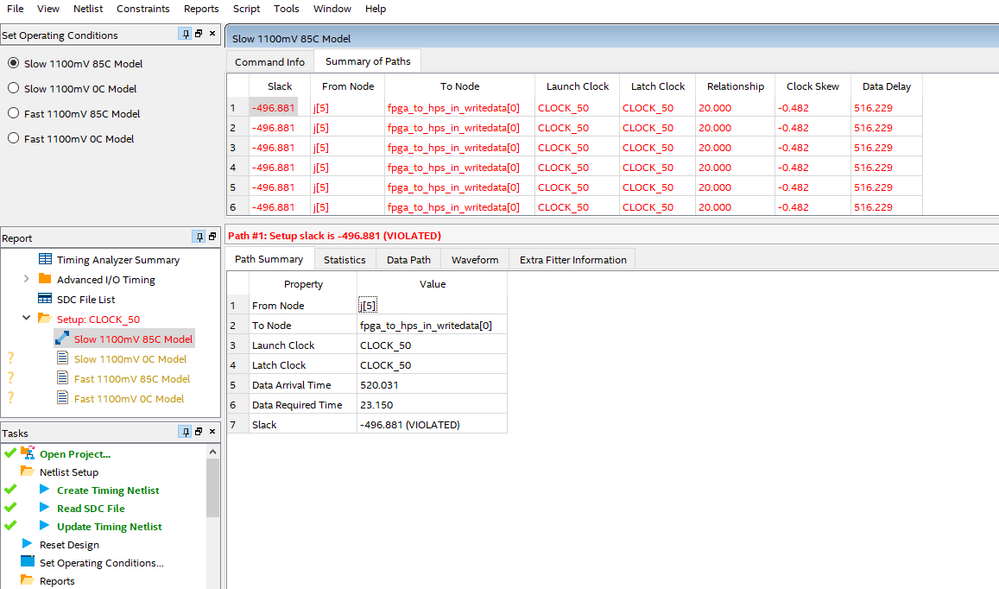

Looking at this issue, it might be caused by the timing issue of your design.

Is the design your own or from a tutorial/ websites that you selected?

Which Quartus version are you currently working on? Could you share your timing reports in Quartus here?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page