- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Intel Support/Expert,

I am learning how to use Arria 10 SoC Development Kit. and planning to purchase a Kit, but I feel really confused with the way Intel document the design files.

from the web address

Intel Arria 10 SX SoC Development Kit

there is a link Intel Arria 10 SX SoC Package Installer (ES2 Edition), I download the package which is called arria10_10as066n3f40e2sge2_soc_v15.1.2.zip. after I unzip it. there are 3 directories.

1. board_design_files. which I can see it is the board design file, like schematic and PCB board file. this is very clear, I believe I can make a duplicate board from here.

2. document, there is only 1 file called ug_a10_soc_dev_kit.pdf, I believe this is a document teach you how to use the board, but not how to use the FPGA.

3. examples. I find many examples seems is teaching how to use FPGA, for example, in sub directory these is transceiver\prd\bts_pcie\bus_pcie.zip. while I compile this bus_pcie project. I got an error message. as a new bee, don't understand what is this mean and how to solve it.

Error (18757): The old Physical Synthesis has been replaced by the Advanced Physical Synthesis for this device family, but there are still Physical Synthesis assignments in the project's Quartus Settings File (.qsf). Support for the following assignments has been discontinued - "PHYSICAL_SYNTHESIS_COMBO_LOGIC, PHYSICAL_SYNTHESIS_REGISTER_DUPLICATION, PHYSICAL_SYNTHESIS_REGISTER_RETIMING".

I couldn't find in this package any guide or application note, explain that how to use this pcie.zip. and there is not an example project that can generate the top .sof file.

as a new guy try to learn the FPGA, is I missed something here? if not then the development kit will have almost no value to me. I can learn how to load the sof file to the board and run test program. what I really need is an FPGA project example which can show me how to generate this .sof file.

To put my question more straight forward, is there any document that tell me in this develop kit how to integrate the PCIe module with the emif. I notice there is a example like

"PCI Express Gen3 x16 AVMM DMA with DDR4 Memory Reference Design ".

I guess it is a example project which include a PCI, DMA and DDR4 module together. but this is only for Stratix 10. not for the Arria dev board.

Thanks,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Regarding the error message, I think this is due to different versions of the Intel Quartus Prime software that you are using and the version used to create the example. Some of the qsf settings in older version are not supported in the newer version.

For reference design, you may find in the link below. User Guides and Reference Designs > Reference design.

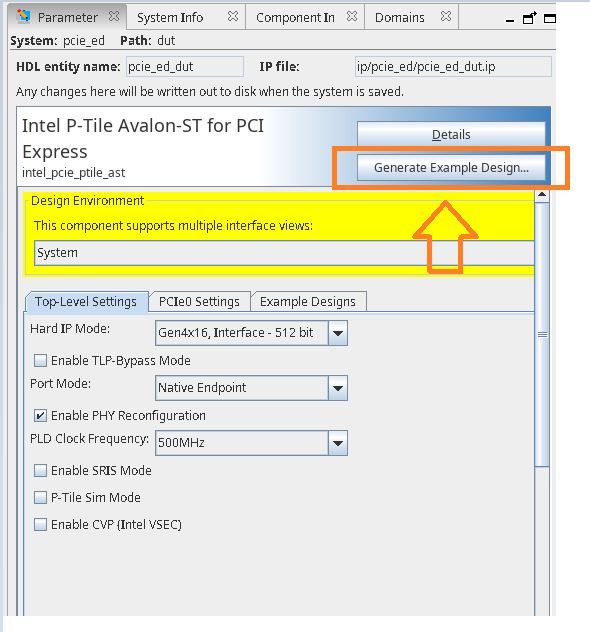

Besides the reference design, you may also generate some simple example designs using the IP parameter setting GUI.

Thanks

Best regards,

KhaiY

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Regarding the error message, I think this is due to different versions of the Intel Quartus Prime software that you are using and the version used to create the example. Some of the qsf settings in older version are not supported in the newer version.

For reference design, you may find in the link below. User Guides and Reference Designs > Reference design.

Besides the reference design, you may also generate some simple example designs using the IP parameter setting GUI.

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY

Even I have many years FPGA design experience, but relatively new to the Platform Designer. Thank you very much for the suggestion.

I followed your link and try to this link

https://www.intel.com/content/dam/altera-www/global/en_US/pdfs/literature/an/an708.pdf

in this document, there is a link

• Arria 10 Reference Design( https://www.alterawiki.com/wiki/Reference_Design:_Gen3x8_AVMM_DMA_with_external_DDR4_-_Arria_10)

To download the reference design and the design software

if I click the Arria 10 Reference design link, I will get this message.

"The requested URL was not found on this server.

Additionally, a 404 Not Found error was encountered while trying to use an ErrorDocument to handle the request."

could you please give a valid link to the <<Arria 10 reference design>> referred in the an708 page 3.

if I can get a full example project which cab be compiled, it will be a very good start point for me to understand PCIe and memory controller.

Best Regards,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY,

After I click Edit the Qsys of the top module, I got the following errors, I think to fully understand this problems, I need to carefully read the emif IP and dma IP user manual, any quick solution.

Error: top.DUT.dma_rd_master/emif_0.ctrl_amm_0: Missing connection start (try "Remove Dangling Connections")

Error: top.DUT.dma_rd_master/DUT.rd_dts_slave: Missing connection start (try "Remove Dangling Connections")

Error: top.DUT.dma_rd_master/DUT.rd_dts_slave: Missing connection end (try "Remove Dangling Connections")

Error: top.DUT.dma_rd_master/DUT.wr_dts_slave: Missing connection start (try "Remove Dangling Connections")

Error: top.DUT.dma_rd_master/DUT.wr_dts_slave: Missing connection end (try "Remove Dangling Connections")

Error: top.DUT.dma_wr_master/mm_clock_crossing_bridge_0.s0: Missing connection start (try "Remove Dangling Connections")

Error: top.DUT.rd_dcm_master/DUT.txs: Missing connection start (try "Remove Dangling Connections")

Error: top.DUT.rd_dcm_master/DUT.txs: Missing connection end (try "Remove Dangling Connections")

Error: top.DUT.rxm_bar4/emif_0.ctrl_amm_0: Missing connection start (try "Remove Dangling Connections")

Error: top.DUT.wr_dcm_master/DUT.txs: Missing connection start (try "Remove Dangling Connections")

Error: top.DUT.wr_dcm_master/DUT.txs: Missing connection end (try "Remove Dangling Connections")

Error: top.DUT.app_nreset_status/clk_0.clk_in_reset: Missing connection start (try "Remove Dangling Connections")

Error: top.DUT.app_nreset_status/emif_0.global_reset_n: Missing connection start (try "Remove Dangling Connections")

Error: top.DUT.app_nreset_status/mm_clock_crossing_bridge_0.s0_reset: Missing connection start (try "Remove Dangling Connections")

Error: top.DUT: DUT.pld_clk must be connected to a clock output

Error: top.DUT.dma_wr_master: Data width must be of power of two and between 8 and 4096

I am just running the example project, why there are still so many errors during loading?

Best,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY,

I following your instruction, and download two example project from Intel,

Arria10_PCIeGen3x8_DMA_18_0.par, for Quatrus Pro, I only have a Standard version, so I couldn't use this example.

AN708_q170.par is this also for Pro version. I can open the project, but when I update the IP automatically.

it will have the errors, like this.

Error: set_parameter_value: No parameter sriov2_exprom_en_hwtcl

while executing

"set_parameter_value $name $value"

(procedure "ip_set_parameter_value" line 6)

invoked from within

"ip_set_parameter_value $name $value"

(procedure "ip_set" line 24)

invoked from within

"ip_set "parameter.$name.value" $value"

(procedure "::altera_pcie_a10_hip::parameters::upgrade" line 28)

invoked from within

"::altera_pcie_a10_hip::parameters::upgrade altera_pcie_a10_hip 17.0 {pf2_bar2_size_hwtcl 12 slave_address_map_4_hwtcl 28 pf0_vf_bar2_size_hwtcl 12 pf0..."

I guess it is also for Quartus Pro version, right? if it also works for standard version, then I got the following error message when I Edit the Qsys top.

Thanks,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

KyaiY

Good new is that after I made the following process, the project pass compilation. but I am not sure the modification I made working or not.

after “remove danling connections" become 4 errors.

Error: top.DUT: DUT.pld_clk must be connected to a clock output

connected to clk0.clk

Error: top.clk_0: clk_0.clk_in_reset must be connected to a reset source

connected to emif_usr_reset_n

Error: top.emif_0: emif_0.global_reset_n must be connected to a reset source

connected to emif_usr_reset_n

Error: top.mm_clock_crossing_bridge_0: mm_clock_crossing_bridge_0.s0_reset must be connected to a reset source

connected to emif_usr_reset_n

regenerate the IP core, pass

----------------------------

commented this line in TOP module.

// .core_clk_out_clk(core_clkout),

I am going to see if I can do some simulation. it will take a while.

Thank you for your help.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY,

I think after a big circle, I am getting close to the target, I download a package from this location

Index of /release/ghrd_release/arria10 (rocketboards.org)

I think this is what I need, if I purchase a Arria 10 SOC gold board.

but it still won't compile.

the warning message is

Warning (125092): Tcl Script File ghrd_10as066n2/ghrd_10as066n2.qip not found

the error message is Error (12006): Node instance "soc_inst" instantiates undefined entity "ghrd_10as066n2". Ensure that required library paths are specified.

this is a whole project downloaded from Intel, any suggestion to link this ghrd_10as066n2 into the design.

Thanks,

David

Info: Running Quartus Prime Analysis & Synthesis

Info: Version 18.1.0 Build 625 09/12/2018 SJ Standard Edition

Info: Processing started: Tue Sep 07 04:22:03 2021

Info: Command: quartus_map --read_settings_files=on --write_settings_files=off ghrd_10as066n2 -c ghrd_10as066n2

Warning (125092): Tcl Script File ghrd_10as066n2/ghrd_10as066n2.qip not found

Info (125063): set_global_assignment -name QIP_FILE ghrd_10as066n2/ghrd_10as066n2.qip

Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.

Info (20030): Parallel compilation is enabled and will use 10 of the 10 processors detected

Info (12021): Found 1 design units, including 1 entities, in source file ghrd_a10_top.v

Info (12023): Found entity 1: ghrd_a10_top

Info (12021): Found 1 design units, including 1 entities, in source file ip/debounce/debounce.v

Info (12023): Found entity 1: debounce

Info (12021): Found 1 design units, including 1 entities, in source file ip/edge_detect/altera_edge_detector.v

Info (12023): Found entity 1: altera_edge_detector

Warning (10236): Verilog HDL Implicit Net warning at altera_edge_detector.v(32): created implicit net for "reset_qual_n"

Info (12127): Elaborating entity "ghrd_a10_top" for the top level hierarchy

Info (12128): Elaborating entity "debounce" for hierarchy "debounce:debounce_inst"

Info (12128): Elaborating entity "altera_edge_detector" for hierarchy "altera_edge_detector:pulse_cold_reset"

Info (12128): Elaborating entity "altera_edge_detector" for hierarchy "altera_edge_detector:pulse_warm_reset"

Info (12128): Elaborating entity "altera_edge_detector" for hierarchy "altera_edge_detector:pulse_debug_reset"

Error (12006): Node instance "soc_inst" instantiates undefined entity "ghrd_10as066n2". Ensure that required library paths are specified correctly, define the specified entity, or change the instantiation. If this entity represents Intel FPGA or third-party IP, generate the synthesis files for the IP.

Error: Quartus Prime Analysis & Synthesis was unsuccessful. 1 error, 3 warnings

Error: Peak virtual memory: 4765 megabytes

Error: Processing ended: Tue Sep 07 04:22:10 2021

Error: Elapsed time: 00:00:07

Error: Total CPU time (on all processors): 00:00:17

Error (293001): Quartus Prime Flow was unsuccessful. 3 errors, 3 warnings

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY,

Good news, after I generate the HDL, then seems it start compile. thank you for all your help.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page