- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Inter support and expert

I am porting a TI demo to Arria GX development board, the original design was a 64bits EMIF. and the DDR module is 72 bits.

to make it simple, I hope I can use 64 bits EMIF directly drive a 72bits module, because I don't care the last 8 bits. I hope this works but I am not sure, can someone who have passed this hassle give me a confirmation.

if I have to change the EMIF interface to 72 bits to match the DDR4 module. then how to handle the 9th byte, as all internal memory bus are based on 8 byte.

Thank you very much.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

In case you're doing some demos, I think it's good for you to create an EMIF example design with Arria 10 Dev Kit preset where you can choose the preset in the EMIF Parameter Editor.

The preset will set the parameter that match to the Arria 10 Dev Kit.

The 72 bits = 64 bits Data + 8 bits ECC.

If you enabled the ECC in your configuration, then you will have 72 bits interface.

Else your interface should be 64 bits.

-Adzim

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The extra byte is for error correction (ECC). The EMIF IP supports this so you just need to enable it when parameterizing the IP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

In case you're doing some demos, I think it's good for you to create an EMIF example design with Arria 10 Dev Kit preset where you can choose the preset in the EMIF Parameter Editor.

The preset will set the parameter that match to the Arria 10 Dev Kit.

The 72 bits = 64 bits Data + 8 bits ECC.

If you enabled the ECC in your configuration, then you will have 72 bits interface.

Else your interface should be 64 bits.

-Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi AdzimZM

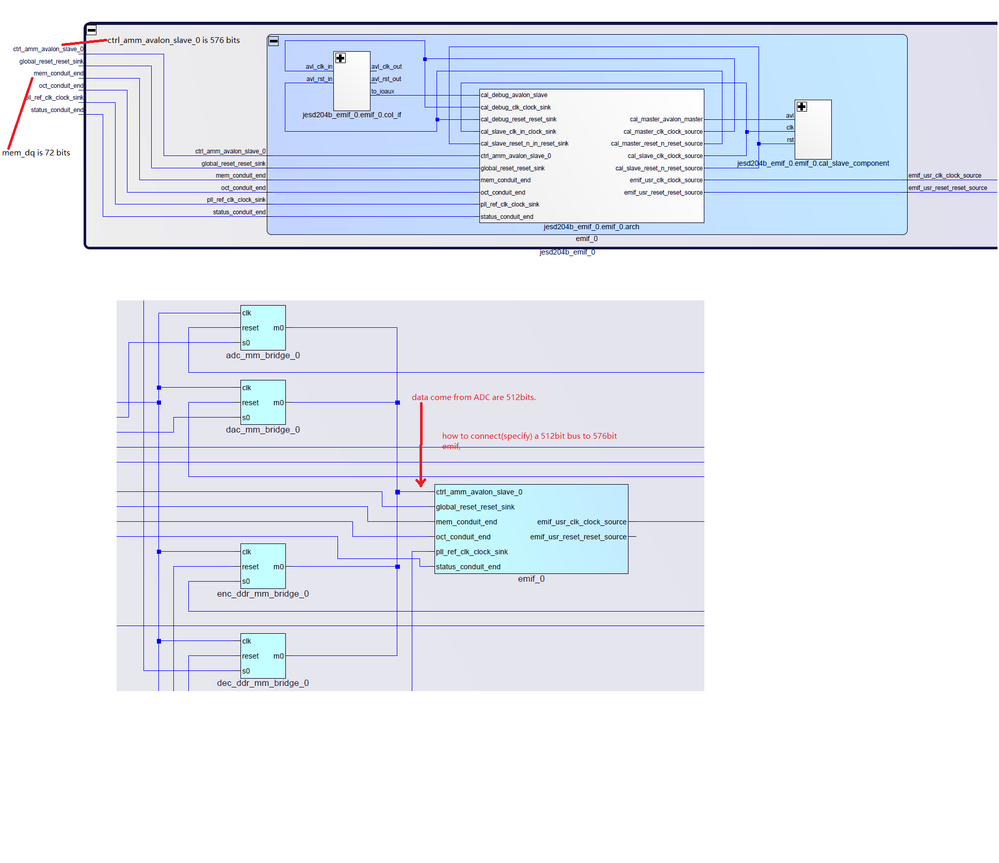

Thank you for your explanation, I have questions while I implement this 72bits EMIF qsys. If I use the presets emif_0 from Arria 10 GX FPGA Development Kit with DDR4 HILO form FPGA(72). as in the picture, the EMIF to Avalon bus will be 576 bits. but the data from the ADC is 512 bits. where and how to convert this 512 bits data to 576 bits.

Thanks

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

if we enable the ECC feature, then the data path to the upstream will be set to 64 instead of 72. thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

I guess your DDR4 design is working correctly.

Kindly let me know if you're facing any error with the memory interface.

Thanks,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim

Yes, I do need to enable the ECC function. it works fine. thank you very much for the following up.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page