Automated EMIF Layout Checks

Änderungen angenommen. Das Abonnement wurde hinzugefügt.

Erfolgreiche Durchführung! Abonnement entfernt.

Sie müssen sich verifizieren, um diese Aktion abzuschließen. Klicken Sie auf den Verifizierungslink in Ihrer E-Mail. Erneut senden über Ihr Profil.

- Intel Community

- Intel Community Wissensdatenbank

- Product Support Forums Wissensdatenbank

- FPGA Wissensdatenbank

- FPGA Wiki

- Automated EMIF Layout Checks

Automated EMIF Layout Checks

- RSS-Feed abonnieren

- Als neu kennzeichnen

- Als gelesen kennzeichnen

- Lesezeichen

- Abonnieren

- Drucker-Anzeigeseite

- Anstößigen Inhalt melden

Automated EMIF Layout Checks

Intro

This wiki pages assumes you have basic familiarity with HyperLynx DRC too. If you would like to learn more about this tool please visit the HyperLynx DRC page.

This page is created to help you test your board layout against Altera External Memory Interfaces (EMIF) guildelines, using MentorGraphics HyperLynx DRC tool. We have identified some of these guidelines to be critical in interface functionality. We also understand that during post layout checks, these guidelines are difficult to manually verify which motivated us to work with Hyperlynx DRC and automate the checking of these critical guidelines. For each of these critical guidelines, we have created custom rules in HyperLynx DRC and are providing the following information to help you better understand the usage and violation reporting of each rule:

Description: A brief overview of which Layout Guideline this rule checks and any other necessary info to help you better understand the guideline.

Input Object List: The input needed to run the rule. For these rules usually means an object list that contains the electrical nets being tested.

Parameters: Parameters allow you to modify some options within the rule. All parameters are by default set to Altera recommended values, but you may test your design at different values when necessary.

Violations: For every violation within each rule a row is added to the violation report with details regarding the violation. In this section,we explain what kind of information is provided with each violation so you can find and fix those violations faster.

Video Tutorial

https://www.youtube.com/watch?v=joaef_YpxGc

HyperLynx DRC Quick Tips & Tricks

How to create an object list and add objects

- In the Project Explorer Menu expand Analysis Setup

- Right Click on Object Lists and select New List

- New list will appear under Object Lists with the name ObjectList_[Number].

- You may rename your Object List by right clicking and selecting Rename

- Next find your desired objects under Project Data

- Select all objects you would like to add to the target list. (You may select multiple objects by holding down the Ctrl key)

- Right-click on one of the selected objects and select copy.

- Open Analysis Setup>Object Lists and locate your target object list

- Right-click on the object list and select paste

- Expand the object list to ensure all intended objects were added

How to import and run custom rules in HyperLynx DRC

- Download the zipped folder (EMIFguidelines.zip) for the rules from the bottom of this page

- Unzip the folder to your computer

- Import your board project into HyperLynx DRC

- In HyperLynx DRC, Expand Rules and Results and right-click on Rules and select New Group

- You may rename the new group to Altera Guidelines or similar names for easier identification.

- Right-click on the new group and select Import Rule. Find the unzipped folder and select all items. Press Open

Now you have imported all the guidelines into HyperLynx DRC. To run a specific rule:

- Click the rule to open the Rule Properties Window right below the Project Explorer

- Find the Object list property in the Rule Properties window and provide the appropriate object list for the rule.

- Select Spreadsheet-[Rule Name] on the tabs at the lower center of the page and select the Parameters tab.

- Provide the necessary input for each parameter. At this point, you should also see a brief description of the rule in the main window

- Go back and select the rule name in the Project Explorer menu, then right-click on it and select Execute.

- The rule will begin running and you can track progress in the right lower corner

- Once the run is finished you may view the violations in the Spreadsheet tab under Violations

To run all rules at once:

- Ensure all necessary object lists and parameters have been provided as described above

- Right-click on the group name (i.e. Altera Guidelines) and select Execute Rules

- You can track the progress on the Group Name by seeing how many rules have finished running

Viewing Violation Reports

- Once a rule is finished executing, click on the rule under Rule Sources in the Project Explorer window

- Select the Spreadsheet tab in the bottom center of the GUI and select the violations tab in the Spreadsheet section

- Here you see the table of violations with different attributes of each violation on different columns

- Each row represents a different error

- You may move columns around by clicking and holding the column title and then dragging it to the right or left.

- You may also sort every column in ascending or descending order by just clicking on the column title.

- For some violations, click on the violation row will give you some extra viewing options to better investigate the violation

- These viewing options appear on the right lower corner of the window in the Details section when you click on each violation row

Altera Rules

Max Length

Description

The length of all electrical nets checked must be within a maximum length specified

Input Object List

The object list of all electrical nets to be checked

Parameters

Maximum Length: Maximum length requirement; i.e., all nets must be less than or equal to this length. Default is 4.5 inches.

Include Package Length: Yes=include package length for length calculation. No= exclude package length for length calculation.

Violations

Net length is longer than maximum length specified

Skew within the Byte Lane Group

Description

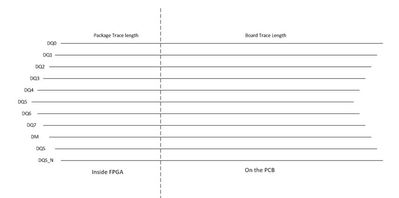

Net delays in a net group must be within the maximum allowed skew. For DQ/DQS/DM signals within a DQS group, default value for max skew is 20ps.

Input Object List

The object list of all DQ/DQS/DM nets to be checked

Parameters

Max Skew: Maximum allowable skew for total delays. Default is 20ps.

Include Package Delay: Yes= include package delay for total net delay calculation.No= do not include package delay for total net delay calculation. You must select Yes here if your board traces compensate for package skew mismatch. If Yes is selected, you must run Add Pin Package Delay script first to provide the necessary info.

Calculate Propagation Delay from Stackup: Yes= propagation velocity is calculated from the field solver using the board stackup information.No= 167 ps/in will be used as signal propagation velocity.

Violations

Net Delay Mismatch:The two identified nets are not within the maximum allowed skew

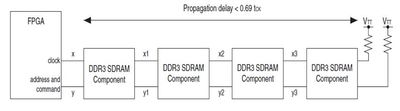

Skew between Addr/Cmd and Mem Clock

Description

All the address and command signals must be delay matched compared to clock traces within the tolerance specified.

x = y +/- 20 ps

x + x1 = y + y1 +/- 20 ps

x + x1 + x2 = y + y1 + y2 +/- 20 ps

x + x1 + x2 + x3 = y + y1 + y2 + y3 +/- 20 ps

Input Object List

None. All necessary information is given to the code through parameters.

Parameters

Reference Object List: The name of the object list containing all the clock traces to which other traces are compared

Target Object Lists: The names of a set of object lists that contain address, command, and control nets. Multiple object lists can be specified using comma separated value format; for example: objList1, objList2.

Maximum Tolerance: Maximum skew allowed for a address, command, or control net to be different from any clock net. The default is 20ps.

Include Package Delay: Yes= include package delay for total net delay calculation; No= do not include package delay for total net delay calculation. You must select Yes here if your board traces compensate for package skew mismatch. If Yes is selected, you must run Add Pin Package Delay script first to provide the necessary info.

Calculate Propagation Delay from Stackup: Yes= propagation velocity is calculated from the field solver using the board stackup information. No= 167 ps/in will be used as signal propagation velocity. Recommendation is to use Yes.

Violations

Delay Matching Violation: The delay of the identified net is greater or less than at least one clock net.

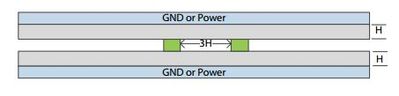

Spacing Guidelines - Data/Data Strobe/Data Mask Signals

Description

Maintain at least 3H spacing between the edges (air-gap) these traces. Where H is the vertical distance to the closest return path for that particular trace.

Input Object List

An object list of all electrical nets to be checked. The object list must only contain Data, Data Strobe, and Data Mask nets.

Parameters

Space Multiple: The number of spaces or H (as mentioned in description) which the code will use to determine whether two traces are too close or not. Space (H) is the distance to the closest return path for the net with a bigger H (out of the two nets being compared). Default value is 3.

Violations

If two nets within the object list have segments that are parallel and closer than minimum distance, then a violation is thrown. The script reports the violating segments with the longest parallel overlap, not the violating segments with the smallest distance between them. If two nets are too close at a point (vs parallel lines) or they cross over each other (on different layers of course), it is not a violation.

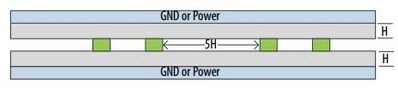

Spacing Guidelines - Address/Command/Clock Signals

Description

For Address/Command/Control traces: Maintain at least 3H spacing between the edges (air-gap) these traces. Where H is the vertical distance to the closest return path for that particular trace.

For Clock traces: Maintain at least 5H spacing between two clock pair or a clock pair and any other memory interface trace. Where H is the vertical distance to the closest return path for that particular trace.

Input Object List

An object list which contains all address, command, and clock nets to be checked. The list must only contain these signals.

Parameters

Space Multiple: The number of spaces (H) which the code will use to determine whether two non-clock traces are too close or not. Space is the distance to the closest return path for the net with a bigger H (out of the two nets being compared). The default value is 3.

Space Multiple for Clock Traces: The number of spaces (H) which the code will use to determine whether a non-clock trace is too close to a clock trace or two clock traces are close to each other. Space(H) is the distance to the closest return path for the net with a bigger H (out of the two nets being compared). The default value is 5.

Violations

If two nets within the object list have segments that are parallel and closer than the minimum distance, then a violation is thrown. The script reports the violating segments with the longest parallel overlap, not the violating segments with the smallest distance between them. If two nets are too close at a point (vs parallel lines) or they cross over each other (on different layers of course), it is not a violation.

CLK-DQS

Description

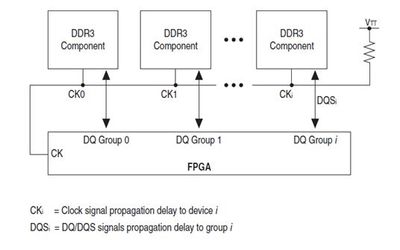

Below mentioned leveling rules are only applicable for fly by typologies only. For now, the DRC tool only allow you to check the leveling rules for Discrete component based interfaces. The DRC tool doesn't have a way to encorporate DIMM delays in to the calculation

The timing between the DQS and clock signals on each device calibrates dynamically to meet tDQSS. To make sure the skew is not too large for the leveling circuit’s capability:

1. Propagation delay of clock signal must not be shorter than propagation delay of DQS signal at every device:

(CKi) – DQSi > 0; 0 < i < number of components – 1

2. Total skew of CLK and DQS signal between groups is less than one clock cycle:

(CKi + DQSi) max – (CKi + DQSi) min < 1 × tCK

If you are using a DIMM topology, your delay and skew must take into consideration value for the actual DIMM.

Input Object List

None. All input information gets provided through parameters.

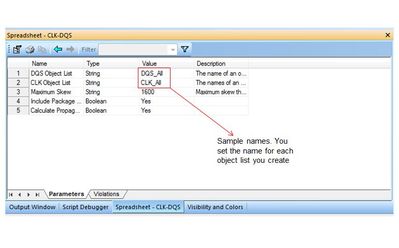

Parameters

DQS Object List: The object list that contains all DQS nets.

CLK Object List: The object list that contains all clock nets

Maximum Skew: Maximum skew allowed for DQSi+CLKi between different groups; the default value is 1600 ps. Please ensure the parameter type is string and you only enter a numerical number in unit of pico seconds

Include Package Delay: Yes= Include package delay for total net delay calculation. No= do not include package delay for total net delay calculation. If Yes is selected, you must run Add Pin Package Delay script first to provide the necessary info.

Calculate Propogation Delay from Stackup: Yes= propagation velocity is calculated from the field solver using the board stack up information. No= 167 ps/in will be used as signal propagation velocity

Violations

DQS after CLK: If delay of the DQS net is greater than any net in the CLK Object List. The error will show you both DQS and clock nets violating this rule as well as the delay difference.

Maximum Skew: If the maximum skew for DQSi + CLKi between different groups exceed maximum skew

Add Pin Package Delay

Description

This rule does not check for any physical violation. This is more like an add on script that you have to run before you run your Data and Address/Command skew matching rules If you have deskewed for package skew mismatch on the PCB, then you must run this rule so the following rules take that into consideration when running. Be sure to run it before running each of the following rules.

- Skew within the Byte Lane Group

- Skew between Addr/Cmd and Mem Clock

If you have not deskewed, then no need to run and please select No for this option at each of the above rules.

Input Object List

None

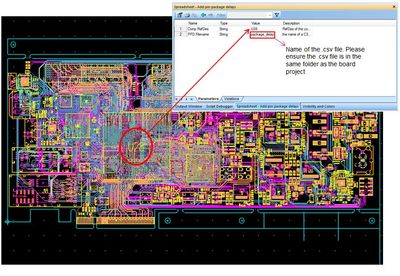

Parameters

Comp RefDes:The reference designator of the FPGA. This is the prefix to all pin names in the targeted FPGA.

PPD Filename:Name of the package file which contains all pin package delays for the specified FPGA. The file must be in CSV format with the following template: Column A = Pin Number, Column B = Total Delays(ps), Column C = Total Length(mm). If you do not have the package delay file or the file you have does not have the above mentioned format then please contact Altera Support.

Violations

If either parameters are left empty, or the file names entered cannot be found within the script folder, a violation is submitted.

Download Guideline Files

Community-Support wird während der normalen Geschäftszeiten (Montag bis Freitag, 7.00 bis 17.00 Uhr PST) angeboten. Andere Kontaktmethoden finden Sie hier.

Intel überprüft nicht alle Lösungen, darunter auch nicht alle Dateiübertragungen, die ggf. in der Community stattfinden. Dementsprechend lehnt Intel alle ausdrücklichen und stillschweigenden Garantien ab, einschließlich und ohne Einschränkung stillschweigender Garantien der Marktgängigkeit, der Eignung für einen bestimmten Zweck und der Nichtverletzung von Rechten sowie jeglicher Garantien, die sich aus der Ausführung, Bearbeitung oder handelsmäßigen Verwendung ergeben.

Vollständige Angaben zu Compiler-Optimierungen finden Sie in unseren Optimierungshinweis.