- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Is there any resource which maps all kinds of x86 instructions to "parsable" pseudo code?

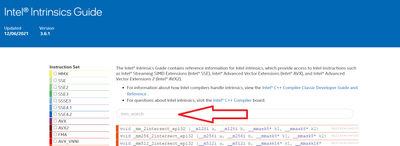

The intrinsics guide has a very clean representation of each intrinsic behavior under Operation.

But I can not find something similar for simple x86 instructions and its extensions.

The instructions pseudo code in the IA-32 manual (SDM Volume 2) is really vague sometimes.

Is there any such resource for asm instruction behavior which matches the clean syntax of the intrinsic behavior?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for posting in Intel communities.

>>” maps all kinds of x86 instructions to "parsable" pseudo code?”

Could you please elaborate on what do you mean by the “parsable” pseudo code?

>> ”The instructions pseudo code in the IA-32 manual (SDM Volume 2) is really vague sometimes.”.

Could you please confirm whether this is the document you are referring to? https://cdrdv2.intel.com/v1/dl/getContent/671200

>> ”Is there any such resource for asm instruction behavior which matches the clean syntax of the intrinsic behavior?”

Could you please let us know the particular intrinsic or instruction that you wanted to know about it? Or you can find the particular intrinsic information and its pseudocode by searching at the top of the intrinsics guide.

Best regards,

Madhu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Madhu!

Thank you for your reply.

>> Could you please confirm whether this is the document you are referring to? https://cdrdv2.intel.com/v1/dl/getContent/671200

Yes indeed. That's the one.

>> Could you please elaborate on what do you mean by the “parsable” pseudo code?

I think about how to uplift the x86 instructions to the intermediate language RZIL. One way to uplift so many instructions would be to take the behavior of each single instruction (written in something C like) and compile it into the intermediate language.

To make this possible the compiler/parser would need a mostly well defined language the instruction behavior is written in.

Here an example:

The PUSHA instruction behavior in the manual looks like this:

IF 64-bit Mode

THEN #UD

FI;

IF OperandSize = 32 (* PUSHAD instruction *)

THEN

Temp := (ESP);

Push(EAX);

Push(ECX);

Push(EDX);

Push(EBX);

Push(Temp);

Push(EBP);

Push(ESI);

Push(EDI);

ELSE (* OperandSize = 16, PUSHA instruction *)

Temp := (SP);

Push(AX);

Push(CX);

Push(DX);

...Syntax like "IF 64-bit Mode" makes it really hard to parse and compile this instruction behavior into an intermediate language.

Another example would be the MASKMOVDQU instruction:

The behavior in the manual is:

IF (MASK[7] = 1)

THEN DEST[DI/EDI] := SRC[7:0] ELSE (* Memory location unchanged *); FI;

IF (MASK[15] = 1)

THEN DEST[DI/EDI +1] := SRC[15:8] ELSE (* Memory location unchanged *); FI;

(* Repeat operation for 3rd through 14th bytes in source operand *)

IF (MASK[127] = 1)

THEN DEST[DI/EDI +15] := SRC[127:120] ELSE (* Memory location unchanged *); FI;The corresponding intrinsic "void _mm_maskmoveu_si128(__m128i d, __m128i n, char * p)" is:

FOR j := 0 to 15

i := j*8

IF mask[i+7]

MEM[mem_addr+i+7:mem_addr+i] := a[i+7:i]

FI

ENDFORThe latter one could be easily parsed and compiled into the intermediate language. The former not so easily.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the inconvenience caused, there are no references available other than Intel® Intrinsics Guide and Intel® 64 and IA-32 Architectures Software Developer Manuals which we have mentioned already in the previous posts.

Thanks and regards,

Madhu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We have not heard back from you. Could you please provide an update on your issue? Can we go ahead and close this thread?

Best regards,

Madhu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As we haven't heard back from you, we assume that you got the required information from us and closing this thread. Please post a new question if you need any additional information from Intel, as this thread will no longer be monitored.

Thanks and regards,

Madhu

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page