- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For the QR decomposition sample, I can not get the right result according to the guidance. There are many errors that happened in the devcloud.

The directory is

oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd

And I use mkdir to get the build directory.

Then use "cmake .. -DFPGA_BOARD=intel_s10sx_pac:pac_s10" to use FPGA D5005 PAC.

And I use "qsub -I -l nodes=1:fpga:ppn=2 -d ." to use this FPGA node.

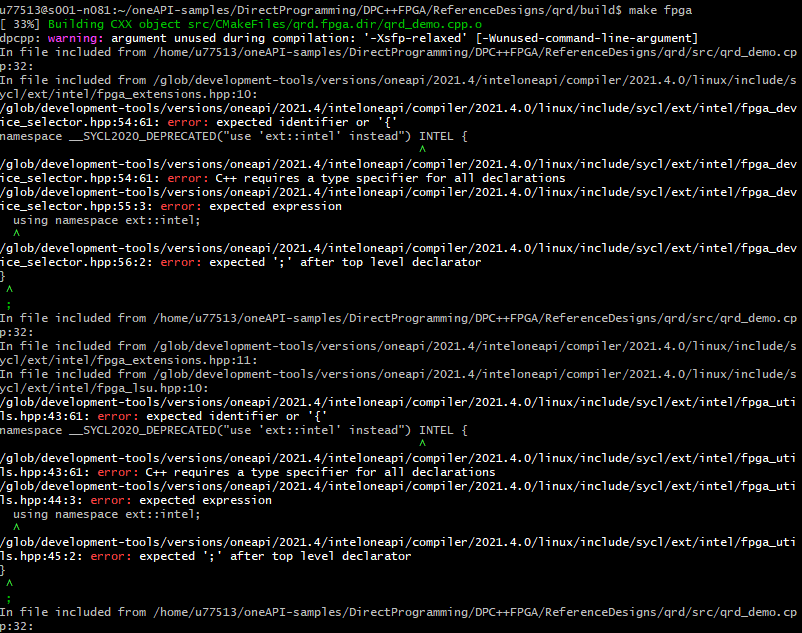

Then "make fpga_emu", but many error emerge.

[ 33%] Building CXX object src/CMakeFiles/qrd.fpga_emu.dir/qrd_demo.cpp.o

In file included from /home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/src/qrd_demo.cpp:32:

In file included from /glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_extensions.hpp:10:

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_device_selector.hpp:54:61: error: expected identifier or '{'

namespace __SYCL2020_DEPRECATED("use 'ext::intel' instead") INTEL {

^

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_device_selector.hpp:54:61: error: C++ requires a type specifier for all declarations

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_device_selector.hpp:55:3: error: expected expression

using namespace ext::intel;

^

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_device_selector.hpp:56:2: error: expected ';' after top level declarator

}

^

;

In file included from /home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/src/qrd_demo.cpp:32:

In file included from /glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_extensions.hpp:11:

In file included from /glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_lsu.hpp:10:

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_utils.hpp:43:61: error: expected identifier or '{'

namespace __SYCL2020_DEPRECATED("use 'ext::intel' instead") INTEL {

^

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_utils.hpp:43:61: error: C++ requires a type specifier for all declarations

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_utils.hpp:44:3: error: expected expression

using namespace ext::intel;

^

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_utils.hpp:45:2: error: expected ';' after top level declarator

}

^

;

In file included from /home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/src/qrd_demo.cpp:32:

In file included from /glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_extensions.hpp:11:

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_lsu.hpp:130:61: error: expected identifier or '{'

namespace __SYCL2020_DEPRECATED("use 'ext::intel' instead") INTEL {

^

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_lsu.hpp:130:61: error: C++ requires a type specifier for all declarations

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_lsu.hpp:131:3: error: expected expression

using namespace ext::intel;

^

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_lsu.hpp:132:2: error: expected ';' after top level declarator

}

^

;

In file included from /home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/src/qrd_demo.cpp:32:

In file included from /glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_extensions.hpp:12:

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_reg.hpp:49:61: error: expected identifier or '{'

namespace __SYCL2020_DEPRECATED("use 'ext::intel' instead") INTEL {

^

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_reg.hpp:49:61: error: C++ requires a type specifier for all declarations

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_reg.hpp:50:3: error: expected expression

using namespace ext::intel;

^

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_reg.hpp:51:2: error: expected ';' after top level declarator

}

^

;

In file included from /home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/src/qrd_demo.cpp:32:

In file included from /glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/fpga_extensions.hpp:13:

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/pipes.hpp:205:61: error: expected identifier or '{'

namespace __SYCL2020_DEPRECATED("use 'ext::intel' instead") INTEL {

^

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/pipes.hpp:205:61: error: C++ requires a type specifier for all declarations

/glob/development-tools/versions/oneapi/2021.4/inteloneapi/compiler/2021.4.0/linux/include/sycl/ext/intel/pipes.hpp:206:3: error: expected expression

using namespace ext::intel;

^

fatal error: too many errors emitted, stopping now [-ferror-limit=]

20 errors generated.

src/CMakeFiles/qrd.fpga_emu.dir/build.make:62: recipe for target 'src/CMakeFiles/qrd.fpga_emu.dir/qrd_demo.cpp.o' failed

make[3]: *** [src/CMakeFiles/qrd.fpga_emu.dir/qrd_demo.cpp.o] Error 1

CMakeFiles/Makefile2:91: recipe for target 'src/CMakeFiles/qrd.fpga_emu.dir/all' failed

make[2]: *** [src/CMakeFiles/qrd.fpga_emu.dir/all] Error 2

CMakeFiles/Makefile2:135: recipe for target 'src/CMakeFiles/fpga_emu.dir/rule' failed

make[1]: *** [src/CMakeFiles/fpga_emu.dir/rule] Error 2

Makefile:131: recipe for target 'fpga_emu' failed

make: *** [fpga_emu] Error 2

So how to solve this problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, @BoonBengT_Intel :

Thanks for your reply.

I have understood the cause of the problem from your description and explanation, but my account still cannot use the devcloud_login command. I will post this problem in another thread here . Thanks again!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @yyjpro

Thank you for posting on the Intel® communities.

We understand that you have some inquiries regarding Intel® DevCloud and FPGA samples. We have a forum for those specific products and questions so we are moving it to the Intel® DevCloud Forum so it can get answered more quickly.

Best regards,

Andrew G.

Intel Customer Support Technician

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I use "qsub -I -l nodes=1:ppn=2 -d ." to compile the FPGA emulator and it succeeds.

and then use "qsub -I -l nodes=1:fpga:ppn=2 -d . " or "qsub -I -l nodes=1:fpga_runtime:ppn=2 -d ." to compile the FPGA hardware, when submit make fpga, they failed.

I want to know why it will happen and how to submit FPGA nodes for compiling hardware correctly. Do they need files like run_ fpga_ hw.sh?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

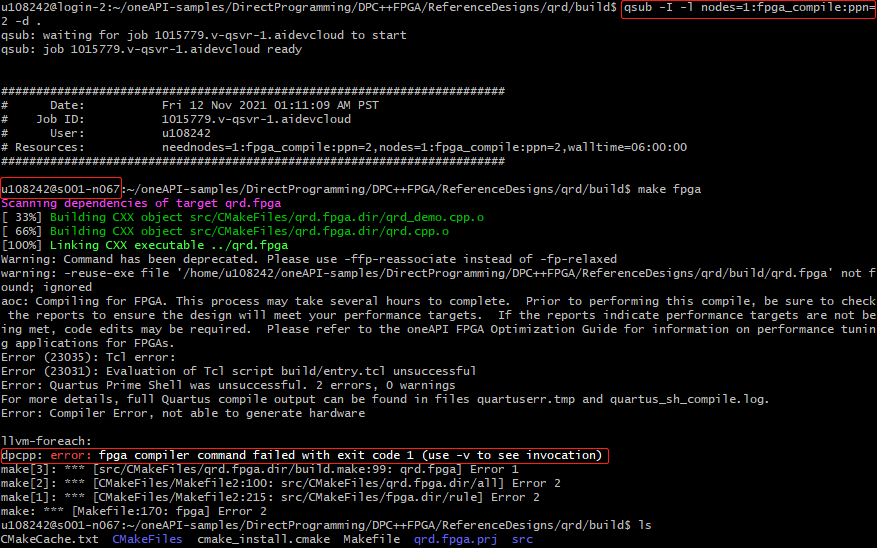

I use fpga_compile to compile the hardware, but also emerges several errors.

make fpga

Scanning dependencies of target qrd.fpga

[ 33%] Building CXX object src/CMakeFiles/qrd.fpga.dir/qrd_demo.cpp.o

[ 66%] Building CXX object src/CMakeFiles/qrd.fpga.dir/qrd.cpp.o

[100%] Linking CXX executable ../qrd.fpga

Warning: Command has been deprecated. Please use -ffp-reassociate instead of -fp-relaxed

warning: -reuse-exe file '/home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/build/qrd.fpga' not found; ignored

aoc: Compiling for FPGA. This process may take several hours to complete. Prior to performing this compile, be sure to check the reports to ensure the design will meet your performance targets. If the reports indicate performance targets are not being met, code edits may be required. Please refer to the oneAPI FPGA Optimization Guide for information on performance tuning applications for FPGAs.

Error (23035): Tcl error:

Error (23031): Evaluation of Tcl script build/entry.tcl unsuccessful

Error: Quartus Prime Shell was unsuccessful. 2 errors, 0 warnings

For more details, full Quartus compile output can be found in files quartuserr.tmp and quartus_sh_compile.log.

Error: Compiler Error, not able to generate hardware

llvm-foreach:

dpcpp: error: fpga compiler command failed with exit code 1 (use -v to see invocation)

make[3]: *** [src/CMakeFiles/qrd.fpga.dir/build.make:99: qrd.fpga] Error 1

make[2]: *** [CMakeFiles/Makefile2:100: src/CMakeFiles/qrd.fpga.dir/all] Error 2

make[1]: *** [CMakeFiles/Makefile2:215: src/CMakeFiles/fpga.dir/rule] Error 2

make: *** [Makefile:170: fpga] Error 2

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, @BoonBengT_Intel :

I am sorry to bother you, I had posted my problems above and solved part of them by myself. BUT I think I need to reorganize those problems here to make it a clear read.

If you could help me to solve and understand the remaining problems, I would be good!

The sample is about QR decomposition in DPC++FPGA.

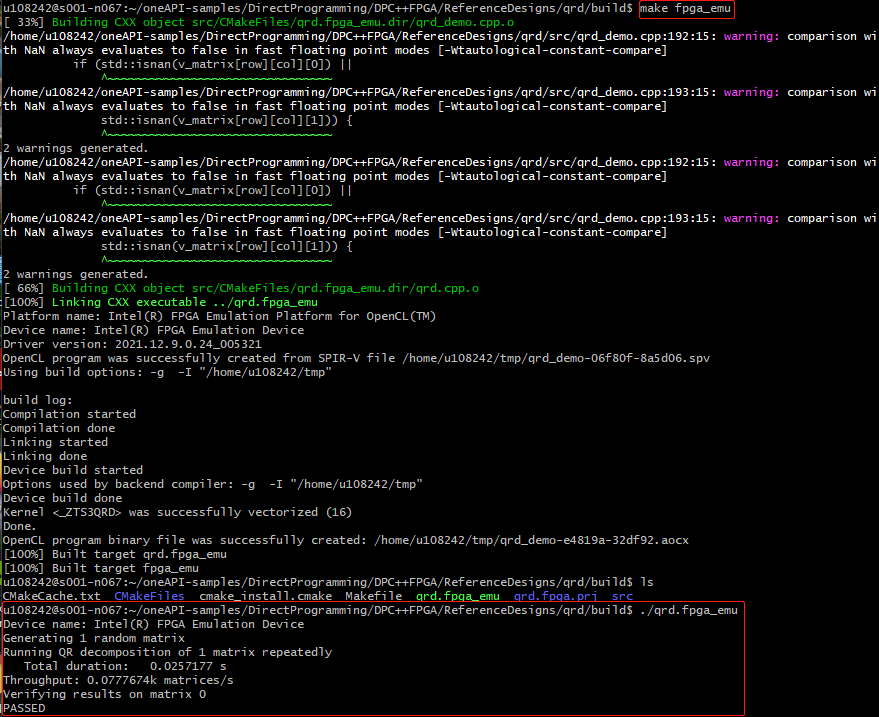

First, I submitted the following node to compile for FPGA emulation successful.

qsub -I -l nodes=1:fpga_compile:ppn=2 -d .

make fpga_emuand here is the result, but I don't know why there are so many warnings. (?)

-- Configuring the design to run on FPGA board intel_s10sx_pac:pac_s10

-- ROWS_COMPONENT=256

-- COLS_COMPONENT=256

-- FIXED_ITERATIONS=105

-- SEED=5

-- Configuring done

-- Generating done

-- Build files have been written to: /home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/build

Scanning dependencies of target qrd.fpga_emu

[ 33%] Building CXX object src/CMakeFiles/qrd.fpga_emu.dir/qrd_demo.cpp.o

/home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/src/qrd_demo.cpp:192:15: warning: comparison with NaN always evaluates to false in fast floating point modes [-Wtautological-constant-compare]

if (std::isnan(v_matrix[row][col][0]) ||

^~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

/home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/src/qrd_demo.cpp:193:15: warning: comparison with NaN always evaluates to false in fast floating point modes [-Wtautological-constant-compare]

std::isnan(v_matrix[row][col][1])) {

^~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

2 warnings generated.

/home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/src/qrd_demo.cpp:192:15: warning: comparison with NaN always evaluates to false in fast floating point modes [-Wtautological-constant-compare]

if (std::isnan(v_matrix[row][col][0]) ||

^~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

/home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/src/qrd_demo.cpp:193:15: warning: comparison with NaN always evaluates to false in fast floating point modes [-Wtautological-constant-compare]

std::isnan(v_matrix[row][col][1])) {

^~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

2 warnings generated.

[ 66%] Building CXX object src/CMakeFiles/qrd.fpga_emu.dir/qrd.cpp.o

[100%] Linking CXX executable ../qrd.fpga_emu

Platform name: Intel(R) FPGA Emulation Platform for OpenCL(TM)

Device name: Intel(R) FPGA Emulation Device

Driver version: 2021.12.9.0.24_005321

OpenCL program was successfully created from SPIR-V file /home/u77513/tmp/qrd_demo-3c97b6-63c7cf.spv

Using build options: -g -I "/home/u77513/tmp"

build log:

Compilation started

Compilation done

Linking started

Linking done

Device build started

Options used by backend compiler: -g -I "/home/u77513/tmp"

Device build done

Kernel <_ZTS3QRD> was successfully vectorized (16)

Done.

OpenCL program binary file was successfully created: /home/u77513/tmp/qrd_demo-f12b0d-bbc0b9.aocx

[100%] Built target qrd.fpga_emu

Scanning dependencies of target fpga_emu

[100%] Built target fpga_emu

Then, I want to compile for FPGA hardware also using the following command.

qsub -I -l nodes=1:fpga_compile:ppn=2 -d .

make fpgaBut the errors happened, as following. Maybe the reason is not every node in devcloud have FPGA hardware ?

Scanning dependencies of target qrd.fpga

[ 33%] Building CXX object src/CMakeFiles/qrd.fpga.dir/qrd_demo.cpp.o

[ 66%] Building CXX object src/CMakeFiles/qrd.fpga.dir/qrd.cpp.o

[100%] Linking CXX executable ../qrd.fpga

Warning: Command has been deprecated. Please use -ffp-reassociate instead of -fp-relaxed

warning: -reuse-exe file '/home/u77513/oneAPI-samples/DirectProgramming/DPC++FPGA/ReferenceDesigns/qrd/build/qrd.fpga' not found; ignored

aoc: Compiling for FPGA. This process may take several hours to complete. Prior to performing this compile, be sure to check the reports to ensure the design will meet your performance targets. If the reports indicate performance targets are not being met, code edits may be required. Please refer to the oneAPI FPGA Optimization Guide for information on performance tuning applications for FPGAs.

Error (23035): Tcl error:

Error (23031): Evaluation of Tcl script build/entry.tcl unsuccessful

Error: Quartus Prime Shell was unsuccessful. 2 errors, 0 warnings

For more details, full Quartus compile output can be found in files quartuserr.tmp and quartus_sh_compile.log.

Error: Compiler Error, not able to generate hardware

llvm-foreach:

dpcpp: error: fpga compiler command failed with exit code 1 (use -v to see invocation)

make[3]: *** [src/CMakeFiles/qrd.fpga.dir/build.make:99: qrd.fpga] Error 1

make[2]: *** [CMakeFiles/Makefile2:100: src/CMakeFiles/qrd.fpga.dir/all] Error 2

make[1]: *** [CMakeFiles/Makefile2:215: src/CMakeFiles/fpga.dir/rule] Error 2

make: *** [Makefile:170: fpga] Error 2

I really look forward to your reply! Thanks so much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

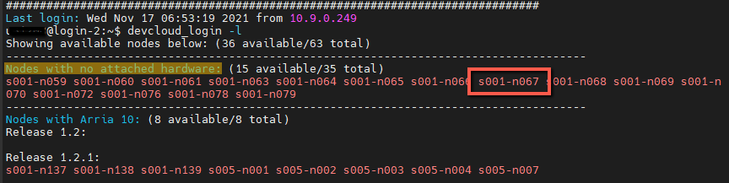

Hi @yyjpro,

Apologies for the delayed in response, for some of the screenshot I can see that the batch job command are executed in the headnodes (i.e. u77513@login-2).

Please try to use the 'devcloud_login' command, followed by selected the appropriate hardware, in this case S10.

Followed by the steps mention in the github guide, and that might work.

Reason being submitting batch job command in the headnodes sometimes will lead to corrupted nodes. (i.e. s001-n081)

Hope that helps.

Best Wishes

BB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, @BoonBengT_Intel :

I tried "devcloud_login" command in the terminal, but it failed.

And I check the resources about this command, and I then found the FPGA-devloud in the Github guide in which it can successfully use this command. So I decide to use FPGA-devcloud. But I cannot register FPGA-devcloud because I couldn't find the register page like https://intelsoftwaresites.secure.force.com/fpgadevcloud And it will go to another devcloud registration page. So does FPGA-devcloud no longer exist?

I really look forward to your reply! Thanks so much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @yyjpro,

Good day, just checking in to see if there is any further doubts in regards to this matter.

Hope we have clarify your doubts.

Best Wishes

BB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, @BoonBengT_Intel :

Thanks for your reply.

I tried the instructions on FPGA-devcloud you gave me and logged in to devcloud using Mobaxterm, but I still can't use FPGA-devcloud. Is it because we can't register FPGA-devcloud now? I have been trying to open the web page in the following figure given by FPGA-devcloud, but I will be directed to the devcloud register web page.

In the MobaXterm, it's the same as Cygwin or VScode. And also cannot use devcloud_login command.

Here I tried several times how to create an FPGA executable(target qrd.fpga) using the FPGA compiler, the nodes are s001-n067, but as before, it failed which shows below. This is the main problem I want to solve.

But FPGA emulator is successful.

I really look forward to your reply! Thanks so much! @BoonBengT_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, @BoonBengT_Intel :

Then I searched Intel website, but I didn't find the registration information about FPGA-devcloud. I remember there was the FPGA-devcloud a few months ago. Is there only devcloud instead of FPGA-devcloud now?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @yyjpro,

The main problem here I see is due to the incorrect node from the qsub command.

For that you would need to use the devcloud_login command to solved that.

As noted on the screenshot error provided, the node 's001-n067' is a nodes with no attached hardware.

Hence the reason why emulation are working and compilation with actual hardware are failing.

That being said, would suggest to create a different thread here to check on the account status/registration.

Hope that clarify and apologies for the inconvenient cause.

Best Wishes

BB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, @BoonBengT_Intel :

Thanks for your reply.

I have understood the cause of the problem from your description and explanation, but my account still cannot use the devcloud_login command. I will post this problem in another thread here . Thanks again!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @yyjpro

,

Greetings, as there is further clarification on what is provided. Hence thread will no longer monitor this thread. For new queries, please feel free to open a new thread and we will be right with you. Pleasure having you here.

Best Wishes

BB

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page