- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

since today I encouter error when compiling for the Arria10 PAC. The build runs fine at the beginning, but crashes near the end of it.

The .o file of the job gives no real hints what's going wrong:

aoc: Compiling for FPGA. This process may take several hours to complete. Prior to performing this compile, be sure to check the reports to ensure the design will meet your performance targets. If the reports indicate performance targets are not being met, code edits may be required. Please refer to the oneAPI FPGA Optimization Guide for information on performance tuning applications for FPGAs.

Error (23035): Tcl error:

Error (23031): Evaluation of Tcl script build/entry.tcl unsuccessful

Error: Quartus Prime Shell was unsuccessful. 2 errors, 0 warningsThe .e file neither:

For more details, full Quartus compile output can be found in files quartuserr.tmp and quartus_sh_compile.log.

Error: Compiler Error, not able to generate hardware

llvm-foreach:

icpx: error: fpga compiler command failed with exit code 1 (use -v to see invocation)

make[3]: *** [cuda/level2/particlefilter/CMakeFiles/particlefilterLib.fpga.dir/build.make:100: cuda/level2/particlefilter/particlefilterLib.fpga] Error 1

make[2]: *** [CMakeFiles/Makefile2:3295: cuda/level2/particlefilter/CMakeFiles/particlefilterLib.fpga.dir/all] Error 2

make[1]: *** [CMakeFiles/Makefile2:2951: cuda/level2/particlefilter/CMakeFiles/particlefilterLib_fpga.dir/rule] Error 2

make: *** [Makefile:1236: particlefilterLib_fpga] Error 2Here a short snippet of the quartus log (complete file as attachement):

Info: Quartus Prime Shell was successful. 0 errors, 237 warnings

Info: Peak virtual memory: 3474 megabytes

Info: Processing ended: Sat Dec 17 05:41:47 2022

Info: Elapsed time: 00:01:38

run.sh: PLL_METADATA/PLL_METADATA_FILE is:

clock-frequency-low:195 clock-frequency-high:390

ERROR: [Errno 2] No such file or directory: './output_files/afu_import.green_region.rbf'

ERROR: packager tool failed to create .gbs file.

Info: *******************************************************************

Info: Running Quartus Prime Shell

Info: Version 19.2.0 Build 57 06/24/2019 SJ Pro Edition

Info: Copyright (C) 2019 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and any partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel FPGA IP License Agreement, or other applicable license

Info: agreement, including, without limitation, that your use is for

Info: the sole purpose of programming logic devices manufactured by

Info: Intel and sold by Intel or its authorized distributors. Please

Info: refer to the applicable agreement for further details, at

Info: https://fpgasoftware.intel.com/eula.

Info: Processing started: Sat Dec 17 04:36:27 2022

Info: Command: quartus_sh -t build/entry.tcl import

Info: Quartus(args): import

Info: Using INI file /home/u153009/tmp/main-4a28c3-d5e0be/quartus.ini

Info: Compiling revision import

Error (23035): Tcl error:

while executing

"qexec "bash build/run.sh $revision_name""

("default" arm line 9)

invoked from within

"switch $tcl_platform(platform) {

windows {

post_message -type error "Full compiles to generate hardware for the FPGA are available on supported ..."

(file "build/entry.tcl" line 36)

Error (23031): Evaluation of Tcl script build/entry.tcl unsuccessful

Error: Quartus Prime Shell was unsuccessful. 2 errors, 0 warnings

Error: Peak virtual memory: 979 megabytes

Error: Processing ended: Sat Dec 17 05:41:49 2022

Error: Elapsed time: 01:05:22Is something wrong with the Quartus-Setup on IntelDevcloud?

Best regards and thanks in advance for your help,

Christoph

- Tags:

- +66623913162

- +66648868871

- 196 จำปาทอง

- 367 จำปาทอง

- choochat118866@gmail.com

- CHOOCHATJUMPATHONG

- สมศักดิ์ จำปาทอง

- สุข จำปาทอง

- สุภาพร จำปาทอง

- เกษม จำปาทอง

- เหลี่ยม จำปาทอง

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Small update: The complete error message in the entry.tcl is the following:

"Full compiles to generate hardware for the FPGA are available on supported Linux platforms only. Please add -rtl to your invocation of aoc to compile without building hardware. Otherwise please run your compile on a supported Linux distribution."So there definitely seems to be something wrong here.

Best regards,

Christoph

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for posting in Intel Communities. Could you please provide us your Sample Reproducer and steps to reproduce your issue so that we can try reproducing your issue from our end?

Regards,

Alekhya

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey Alekhya,

this occur on all builds. I also tried the GettingStarted/Fpga_Compile example from the OneApi Samples github repo - the error occurs also there.

(Also when compiling the tutorial, I noticed there is something wrong with your header-files. I needed to remove

and the default exception-handler.)

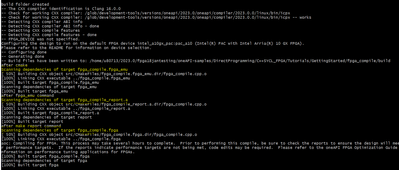

u153009@s001-n068:~/oneAPI-samples/DirectProgramming/DPC++FPGA/Tutorials/GettingStarted/fpga_compile/build$ make fpga

Scanning dependencies of target fpga_compile.fpga

[ 50%] Building CXX object src/CMakeFiles/fpga_compile.fpga.dir/fpga_compile.cpp.o

/home/u153009/oneAPI-samples/DirectProgramming/DPC++FPGA/Tutorials/GettingStarted/fpga_compile/src/fpga_compile.cpp:50:11: warning: unused type alias 'T' [-Wunused-local-typedef]

using T = int;

^

1 warning generated.

/home/u153009/oneAPI-samples/DirectProgramming/DPC++FPGA/Tutorials/GettingStarted/fpga_compile/src/fpga_compile.cpp:50:11: warning: unused type alias 'T' [-Wunused-local-typedef]

using T = int;

^

1 warning generated.

[100%] Linking CXX executable ../fpga_compile.fpga

aoc: Compiling for FPGA. This process may take several hours to complete. Prior to performing this compile, be sure to check the reports to ensure the design will meet your performance targets. If the reports indicate performance targets are not being met, code edits may be required. Please refer to the oneAPI FPGA Optimization Guide for information on performance tuning applications for FPGAs.

Error (23035): Tcl error:

Error (23031): Evaluation of Tcl script build/entry.tcl unsuccessful

Error: Quartus Prime Shell was unsuccessful. 2 errors, 0 warnings

For more details, full Quartus compile output can be found in files quartuserr.tmp and quartus_sh_compile.log.

Error: Compiler Error, not able to generate hardware

llvm-foreach:

dpcpp: error: fpga compiler command failed with exit code 1 (use -v to see invocation)

make[3]: *** [src/CMakeFiles/fpga_compile.fpga.dir/build.make:84: fpga_compile.fpga] Error 1

make[2]: *** [CMakeFiles/Makefile2:100: src/CMakeFiles/fpga_compile.fpga.dir/all] Error 2

make[1]: *** [CMakeFiles/Makefile2:161: src/CMakeFiles/fpga.dir/rule] Error 2

make: *** [Makefile:144: fpga] Error 2- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am also having the same issue. The project folder is created as well as the reports, but no executable is generated and when I check the compile log I get the same situation. I've tried compiling multiple files so I don't think the problem is a bug in my code. I added a copy of the compile log as an annex.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Any updates to this issue? Would be great if this could be fixed before the holidays...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, is there any update for this ? I am also getting the same error messages for all the arria10 oneapi nodes for my own project and also for the default examples from the github DPC++FPGA folder

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

We could reproduce your issue. We are working on this internally. We will get back to you soon with an update.

Regards,

Alekhya

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey @AlekhyaV_Intel ,

are there any updates to this? Or any work around so I can start working again on my projects using the Arria10 FPGA? Would be really great if this could be fixed soon, as I have some deadlines to face during my thesis I currently work on.

Best regards,

Christoph

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The compilation is still not working for Arria10 and Stratix10 FPGAs I have tried s001-n142 and this is the error still. This issue started when the oneAPI is upgraded to 2023 version

llvm-foreach:

icpx: error: fpga compiler command failed with exit code 1 (use -v to see invocation)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey all,

Any updates to this? I tried loading older OneApi versions but still the same error. FPGA builds are now broken for nearly 3 weeks and I really need to continue my compiles for my master-thesis...

Isn't there any temporary workaround or better: Just a rollback of the quartus-version on the compile-nodes?

Thanks in advance,

Christoph

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm having the same problem. Everything works fine for emulator or to get the reports, but it fails when I try to use the FPGA. I can't even compile the given examples.

Any solutions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey Sue,

I have no solutions, even on the arria10-nodes this error occurs mostly. I am unable to compile for nearly a month now.

Just hoping that the Intel representatives don't ignore this thread for another month...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am also having the same issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

Our sincere apologies for the delay. We will update you once we find the resolution.

Regards,

Alekhya

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am running into the same issue with both the dpcpp and icpx -fsycl driver. Hopefully, this can be fixed soon.

Cheers,

Rob

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

I would like to add that I have been having this issue since November. I work with OpenCL instead of DPC++, and I am facing equivalent problems and error messages. I made two community posts about it back when I started having problems; one for Arria 10 and the other for Stratix 10 (at first I thought they were different issues).

For completeness, the links to those community posts are:

In my case, when compiling for Stratix 10, I recurringly see the following error message in addition to the build/entry.tcl one:

Error (16556): The synthesis RTL for ip/ddr_board/ddr_board_acl_memory_bank_divider_1.ip has not been generated. Generate the synthesis RTL form within Platform Designer.

Maybe it provides more insight into the issue.

I apologize for not seeing this community post earlier so I could add my experience and help with the solutions. I thought my posts were the only ones about this topic (as they were for about a month), so I eventually stopped looking for the solution in other posts.

Thanks for the help. I hope the issue is resolved soon.

Manuel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello@hareesh

Seems like there is already another post (this one) reporting my issue, and there are people already working on a solution for it. So I won't be creating a new post/case.

Please, if you could before closing my post/case, indicate that this post is reporting the same issue, and that it is only closed because it is a duplicate, not because it was solved.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Is there any update to this problem ? I couldn't work on my project still and It's more than a month now!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

We apologize for the inconvenience caused. We understand your concern. We have escalated this issue to the admin team. They're working on it internally. We will get back to you soo with an update.

Regards,

Alekhya

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

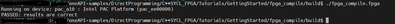

Hi @Christoph9 @filipeborralho @bxbxf @Sue2 @AnaWilliam850 @robertszafa @Mdcc_UVa ,

Thank you all for your patience and we sincerely apologize for the inconvenience caused. The Admin team has been trying to resolve this issue and it's finally fixed on Arria10 oneAPI and Stratix10 oneAPI nodes. We have tested and verified that the below samples are working fine.

Stratix10 (fpga_compile, fast_recompile), Arria10 (fpga_compile, fast_recompile, simple-add, vector-add) samples are working fine

https://github.com/oneapi-src/oneAPI-samples/tree/master/DirectProgramming/C%2B%2BSYCL_FPGA/Tutorials/GettingStarted

https://github.com/oneapi-src/oneAPI-samples/tree/master/DirectProgramming/C%2B%2BSYCL/DenseLinearAlgebra

Could you please check it from your side and let us know if the issue still persists?

If this resolves your issue, make sure to accept it as a solution. This helps others with similar issue. Thank you!

Regards,

Alekhya

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page