- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've generated a design using HLS and is trying to simulate the design using vcs script generated by HLS in the verification directory. But it is throwing syntax errors while compiling the code.

The same codes were compiled properly using modelsim

Any tips to work around this issue will be really helpful

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Please mention the error messages and provide the screenshots for us to get us a better understanding of the error.

Also since the design is working fine , and the modelsim simulation is also working fine , this might not be related to and issue with HLS as such. You may have to look at how the vcs is setup.

Thanks and Regards

Anil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Steps followed:

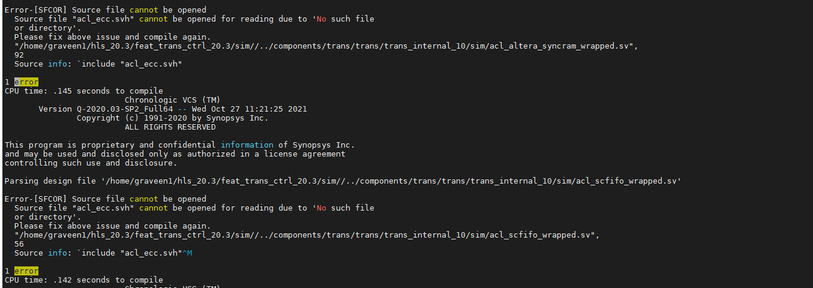

I took the vcsmx_setup.sh script followed the steps mentioned in the script to create new top level script with my RTL files as well and tried compilation. But this is the error I'm getting

Include files are not found for hls generated codes. There are some syntax related error as well.

This is my top level script

#QSYS_SIMDIR is used in the Quartus-generated IP simulation script to

# # construct paths to the files required to simulate the IP in your Quartus

# # project. By default, the IP script assumes that you are launching the

# # simulator from the IP script location. If launching from another

# # location, set QSYS_SIMDIR to the output directory you specified when you

# # generated the IP script, relative to the directory from which you launch

# # the simulator. In this case, you must also copy the generated library

# # setup "synopsys_sim.setup" into the location from which you launch the

# # simulator, or incorporate into any existing library setup.

# #

# # Run Quartus-generated IP simulation script once to compile Quartus EDA

# # simulation libraries and Quartus-generated IP simulation files, and copy

# # any ROM/RAM initialization files to the simulation directory.

# #

# # - If necessary, specify any compilation options:

# # USER_DEFINED_COMPILE_OPTIONS

# # USER_DEFINED_VHDL_COMPILE_OPTIONS applied to vhdl compiler

# # USER_DEFINED_VERILOG_COMPILE_OPTIONS applied to verilog compiler

# #

source /home/graveen1/hls_20.3/feat_trans_ctrl_20.3/sim/synopsys/vcsmx/vcsmx_setup.sh \

SKIP_ELAB=1 \

SKIP_SIM=1 \

# USER_DEFINED_COMPILE_OPTIONS=<compilation options for your design> \

# USER_DEFINED_VHDL_COMPILE_OPTIONS=<VHDL compilation options for your design> \

USER_DEFINED_VERILOG_COMPILE_OPTIONS= -assert svaext

QSYS_SIMDIR=/home/graveen1/hls_20.3/feat_trans_ctrl_20.3/sim/

#USER_DEFINED_ELAB_OPTIONS="'-assert svaext'"

# #

# # Compile all design files and testbench files, including the top level.

# # (These are all the files required for simulation other than the files

# # compiled by the IP script)

# #

vlogan -timescale=1ns/1ns -f ./verilogfiles.txt -top feat_tran_tb -sverilog +incdir+"/home/graveen1/hls_20.3/feat_trans_ctrl_20.3/sim/synopsys/vcsmx/libraries" +incdir+"/home/graveen1/hls_20.3/feat_trans_ctrl_20.3/" | tee comp_rtl.log

# #

# # TOP_LEVEL_NAME is used in this script to set the top-level simulation or

# # testbench module/entity name.

# #

# # Run the IP script again to elaborate and simulate the top level:

# # - Specify TOP_LEVEL_NAME and USER_DEFINED_ELAB_OPTIONS.

# # - Override the default USER_DEFINED_SIM_OPTIONS. For example, to run

# # until $finish(), set to an empty string: USER_DEFINED_SIM_OPTIONS="".

# #

source /home/graveen1/hls_20.3/feat_trans_ctrl_20.3/sim/synopsys/vcsmx/vcsmx_setup.sh \

SKIP_FILE_COPY=1 \

SKIP_DEV_COM=1 \

SKIP_COM=1 \

TOP_LEVEL_NAME="'-top feat_tran_tb'" \

QSYS_SIMDIR=/home/graveen1/hls_20.3/feat_trans_ctrl_20.3/sim/ \

USER_DEFINED_ELAB_OPTIONS="'-sverilog'" \

USER_DEFINED_SIM_OPTIONS=""

# #

~

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page