- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

For the same quartus project,

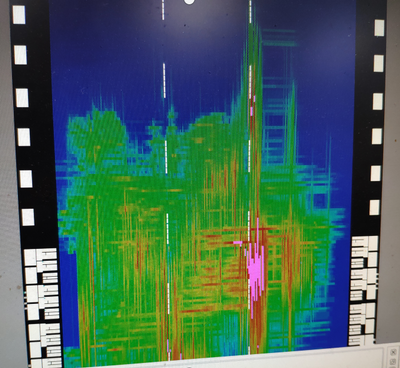

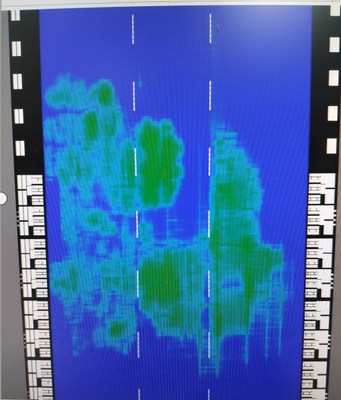

I found that the routing hotspots is different for the pof file got from V16.0 and V18.0, as follow two pictures :

v18.0

V16.0

From above two picture, the routing hotspots got from V16.0 is better compared to the one got V18.0 (many part exceeds 95%), I compared the advanced settings of these two version software:

For synthesis:

For V16.0, it has "Synthesis migration checks for stratix 10 " and V18.0 has no this item;

For V18.0, it has "Allow Register Dupilation" and "Allow Register Merging" and V16.0 does not see these item (maybe it enable these defaultly)

For advanced fitter,

For V16.0, it has " i/o placement optimization" and " Spectra-Q physical Synthesis" and V18.0 has no these item;

For V18.0, it has " Allow register Dupilation" and "Allow Register Merging" and V16.0 has no these item(maybe it enable these defaultly).

Besides above difference, other item is same for V16.0 and V18.0.

So, For V18.0, I closed the "Allow register Dupilation" and "Allow Register Mergin" Item, but the routing hotspots change more worse.

Could you tell me the difference for the complication between V16.0 and V18.0, and is there solution for that I can got the routing hotspots (got V18.0) same as V16.0?

FPGA : 10AX115N2F45E1SG

Brs,

Lambert

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @lambert_yu

V16.0 was released 6 years ago so I not really sure what changes as compared to V18.0.

Have you try to run in the latest Quartus version V21.3 and see if the routing get better?

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi RichardTanSY,

I have not installed V21.3 and If I want, I need to apply for this, it's not convenient.

And I can provide additional information, one project like the above which use more less resource and its routing hotspots got from V17.1 is like to V18.0, so I inferred that the strategy is changed from V17.

Brs,

Lambert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @lambert_yu

Sorry for the late response.

Could you share the projects (v16.0 and v18.0) that can duplicate these behaviour?

Will need to check this with the engineering team.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Richard,

I'm so sorry that I have no authority to share the RTL code to you.

And I can only tell you some information about this project:

first resource (based on 10ax115)

ALM : 21%; Total register : 125543; Total block memory bits 1%; HSSI RX channel 8/48 (17%); Total HSSI TX Channel 4/48 (8%); Total PLLs 57/112 (51%).

For transceiver : 4 Simplex RX IP (each have 4 channel); 2 Simplex TX IP (each have 2 channel). And all IP all located in different banks.

Second,

I think you could use one bigger project like above and maybe the result as the picture which I show above, thanks.

Brs,

Lambert

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page