- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have following error while Analysis & Synthesis using Qyartus 21.2 and 22.2:

Error(13224): Verilog HDL or VHDL error at vector_capture.sv(143): index -8 is out of range [15:0] for 's_in_data'

I have added my project (vector_capture_21_2). The project can be found in vector_capture_21_2\quartus_proj and source files can be found in vector_capture_21_2\src

According to my code and parameter assignments, the index cannot be -8, but I am not clear how the tool see -8 as an index.

Can someone help me to overcome this issue?

Thank you,

Ranesh

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Ranesh ,

The reason for the error is the value of parameter W_MODULE_DATA (256) in submodule vector_capture.sv being overridden by the value of parameter W_MODULE_DATA (16) in top-module vector_capture_synth_top.sv.

Thanks,

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

Thank you for your answer.

What you are saying is correct, but that cannot be the reason for this error message.

From lines 26 and 27 of vector_capture_synth.sv

26: parameter W_MODULE_DATA = 16; // Supported data widths (8 bits to 256 bits) power of 2 (2^3 to 2^8)

27: parameter W_MODULE_DESC = 204; // less than or equal to 256

From lines 66 to 70 of vector_capture.sv are:

66: localparam c_DESCBYTEALIGNBITS = ((W_MODULE_DESC %

c_DESCBYTEALIGNBITS = ((204 %

c_DESCBYTEALIGNBITS = 4

67: logic [((W_MODULE_DESC + c_DESCBYTEALIGNBITS) - 1):0] s_in_desc; // Configuration bus from feeder module

logic [((204 + 4) -1):0] s_in_des

logic [207:0] s_in_des

68: localparam c_IN_DESC_BYTE_CNT = ((W_MODULE_DESC + c_DESCBYTEALIGNBITS)/8);

c_IN_DESC_BYTE_CNT = ((204 + 4)/8)

c_IN_DESC_BYTE_CNT = ((208)/8)

c_IN_DESC_BYTE_CNT = 26

69: localparam c_IN_DATA_BYTE_CNT = (W_MODULE_DATA/8);

c_IN_DATA_BYTE_CNT = (16/8)

c_IN_DATA_BYTE_CNT = 2

70: localparam c_OUT_DATA_BYTE_CNT = (W_MCDMA_DATA/8);

c_OUT_DATA_BYTE_CNT = (256/8)

c_OUT_DATA_BYTE_CNT = 32

The lines 140 and 144 are in vector_capture.sv are:

140: for (int c = c_IN_DESC_BYTE_CNT; c < c_OUT_DATA_BYTE_CNT; c++)

(int c = 26; c < 32; c++)

c can take only 26, 27, 28, 29, 30 and 31

141: begin

142: if (c < (c_IN_DESC_BYTE_CNT + (c_IN_DATA_BYTE_CNT - s_in_empty)))

(c < (26 + (2 - s_in_empty)))

(c < (28 - s_in_empty))

if s_in_empty is 0

c can take only 26 and 27

if s_in_empty is 1

c can take only 26

143: s_output_data[c] <= s_in_data[((W_MODULE_DATA - ((c - c_IN_DESC_BYTE_CNT) * 8)) - 1) -: 8];

If c become 26, the line becomes

s_output_data[26] <= s_in_data[((16 - ((26 - 26) * 8)) - 1) -: 8]

s_output_data[26] <= s_in_data[((16 - ((0) * 8)) - 1) -: 8]

s_output_data[26] <= s_in_data[((16 - 0 - 1) -: 8]

s_output_data[26] <= s_in_data[15 -: 8]

s_output_data[26] <= s_in_data[15 : 8]

If c become 27, the line becomes

s_output_data[27] <= s_in_data[((16 - ((27 - 26) * 8)) - 1) -: 8]

s_output_data[27] <= s_in_data[((16 - ((1) * 8)) - 1) -: 8]

s_output_data[27] <= s_in_data[((16 - 8 - 1) -: 8]

s_output_data[27] <= s_in_data[7 -: 8]

s_output_data[27] <= s_in_data[7 : 0]

144: end

From the above calculations, c cannot take any values that drives the index of s_in_data to be -8.

Regards,

Ranesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

Thank you for your answer.

What you are saying is correct, but it cannot be the cause of this error.

==========

Lines 21, 26 and 27 of vector_capture_synth_top.sv are:

21: parameter W_MCDMA_DATA = 256;

26: parameter W_MODULE_DATA = 16; // Supported data widths (8 bits to 256 bits) power of 2 (2^3 to 2^8)

27: parameter W_MODULE_DESC = 204; // less than or equal to 256

==========

Lines 66 to 70 of vector_capture.sv are:

66: localparam c_DESCBYTEALIGNBITS = ((W_MODULE_DESC %

c_DESCBYTEALIGNBITS = ((204 %

c_DESCBYTEALIGNBITS = (4 > 0) ? (8 - 4) : 3'b0

c_DESCBYTEALIGNBITS = 4

67: logic [((W_MODULE_DESC + c_DESCBYTEALIGNBITS) - 1):0] s_in_desc; // Configuration bus from feeder module

logic [((204 + 4) - 1):0] s_in_desc;

logic [207:0] s_in_desc;

68: localparam c_IN_DESC_BYTE_CNT = ((W_MODULE_DESC + c_DESCBYTEALIGNBITS)/8);

c_IN_DESC_BYTE_CNT = ((204 + 4)/8)

c_IN_DESC_BYTE_CNT = ((208)/8)

c_IN_DESC_BYTE_CNT = 26

69: localparam c_IN_DATA_BYTE_CNT = (W_MODULE_DATA/8);

c_IN_DATA_BYTE_CNT = (16/8)

c_IN_DATA_BYTE_CNT = 2

70: localparam c_OUT_DATA_BYTE_CNT = (W_MCDMA_DATA/8);

c_OUT_DATA_BYTE_CNT = (256/8)

c_OUT_DATA_BYTE_CNT = 32

==========

Lines 140 to 144 of vector_capture.sv are:

140: for (int c = c_IN_DESC_BYTE_CNT; c < c_OUT_DATA_BYTE_CNT; c++)

(int c = 26; c < 32; c++)

Within this for loop, c can take only 26, 27, 28, 29, 30 and 31

141: begin

142: if (c < (c_IN_DESC_BYTE_CNT + (c_IN_DATA_BYTE_CNT - s_in_empty)))

(c < (26 + (2 - s_in_empty)))

(c < (28 - s_in_empty))

Note: s_in_empty is a single bit.

Within this if statement:

If s_in_empty = 0, (c < (28 - 0)) and c can be either 26 or 27

If s_in_empty = 1, (c < (28 - 1)) and c can be either 26

143: s_output_data[c] <= s_in_data[((W_MODULE_DATA - ((c - c_IN_DESC_BYTE_CNT) * 8)) - 1) -: 8];

If c takes 26

s_output_data[26] <= s_in_data[((16 - ((26 - 26) * 8)) - 1) -: 8];

s_output_data[26] <= s_in_data[((16 - ((0) * 8)) - 1) -: 8];

s_output_data[26] <= s_in_data[((16 - (0) - 1) -: 8];

s_output_data[26] <= s_in_data[((16 - 1) -: 8];

s_output_data[26] <= s_in_data[15 -: 8];

s_output_data[26] <= s_in_data[15 : 8];

If c takes 27

s_output_data[26] <= s_in_data[((16 - ((27 - 26) * 8)) - 1) -: 8];

s_output_data[26] <= s_in_data[((16 - ((1) * 8)) - 1) -: 8];

s_output_data[26] <= s_in_data[((16 - (8) - 1) -: 8];

s_output_data[26] <= s_in_data[((8 - 1) -: 8];

s_output_data[26] <= s_in_data[7 -: 8];

s_output_data[26] <= s_in_data[7 : 0];

144: end

From the above calculations, c cannot take any values that drives index of s_in_data to be -8.

Regards,

Ranesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

Thank you for your answer.

What you are saying is correct, but it cannot be the cause of this error.

==========

Lines 21, 26 and 27 of vector_capture_synth_top.sv are:

21: parameter W_MCDMA_DATA = 256;

26: parameter W_MODULE_DATA = 16; // Supported data widths (8 bits to 256 bits) power of 2 (2^3 to 2^8)

27: parameter W_MODULE_DESC = 204; // less than or equal to 256

==========

Lines 66 to 70 of vector_capture.sv are:

66: localparam c_DESCBYTEALIGNBITS = ((W_MODULE_DESC %

c_DESCBYTEALIGNBITS = ((204 %

c_DESCBYTEALIGNBITS = (4 > 0) ? (8 - 4) : 3'b0

c_DESCBYTEALIGNBITS = 4

67: logic [((W_MODULE_DESC + c_DESCBYTEALIGNBITS) - 1):0] s_in_desc; // Configuration bus from feeder module

logic [((204 + 4) - 1):0] s_in_desc;

logic [207:0] s_in_desc;

68: localparam c_IN_DESC_BYTE_CNT = ((W_MODULE_DESC + c_DESCBYTEALIGNBITS)/8);

c_IN_DESC_BYTE_CNT = ((204 + 4)/8)

c_IN_DESC_BYTE_CNT = ((208)/8)

c_IN_DESC_BYTE_CNT = 26

69: localparam c_IN_DATA_BYTE_CNT = (W_MODULE_DATA/8);

c_IN_DATA_BYTE_CNT = (16/8)

c_IN_DATA_BYTE_CNT = 2

70: localparam c_OUT_DATA_BYTE_CNT = (W_MCDMA_DATA/8);

c_OUT_DATA_BYTE_CNT = (256/8)

c_OUT_DATA_BYTE_CNT = 32

==========

Lines 140 to 144 of vector_capture.sv are:

140: for (int c = c_IN_DESC_BYTE_CNT; c < c_OUT_DATA_BYTE_CNT; c++)

(int c = 26; c < 32; c++)

Within this for loop, c can take only 26, 27, 28, 29, 30 and 31

141: begin

142: if (c < (c_IN_DESC_BYTE_CNT + (c_IN_DATA_BYTE_CNT - s_in_empty)))

(c < (26 + (2 - s_in_empty)))

(c < (28 - s_in_empty))

Note: s_in_empty is a single bit.

Within this if statement:

If s_in_empty = 0, (c < (28 - 0)) and c can be either 26 or 27

If s_in_empty = 1, (c < (28 - 1)) and c can be either 26

143: s_output_data[c] <= s_in_data[((W_MODULE_DATA - ((c - c_IN_DESC_BYTE_CNT) * 8)) - 1) -: 8];

If c takes 26

s_output_data[26] <= s_in_data[((16 - ((26 - 26) * 8)) - 1) -: 8];

s_output_data[26] <= s_in_data[((16 - ((0) * 8)) - 1) -: 8];

s_output_data[26] <= s_in_data[((16 - (0) - 1) -: 8];

s_output_data[26] <= s_in_data[((16 - 1) -: 8];

s_output_data[26] <= s_in_data[15 -: 8];

s_output_data[26] <= s_in_data[15 : 8];

If c takes 27

s_output_data[26] <= s_in_data[((16 - ((27 - 26) * 8)) - 1) -: 8];

s_output_data[26] <= s_in_data[((16 - ((1) * 8)) - 1) -: 8];

s_output_data[26] <= s_in_data[((16 - (8) - 1) -: 8];

s_output_data[26] <= s_in_data[((8 - 1) -: 8];

s_output_data[26] <= s_in_data[7 -: 8];

s_output_data[26] <= s_in_data[7 : 0];

144: end

From the above calculations, c cannot take any values that drives index of s_in_data to be -8.

Regards,

Ranesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Ranesh ,

I further create a test case with minimized code.

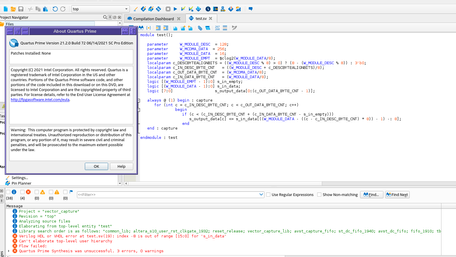

I'm getting synthesis error Error(13224): Verilog HDL or VHDL error at test.sv(19): index -8 is out of range [15:0] for 's_in_data' as you mentioned before in Quartus Pro v21.2 check image:

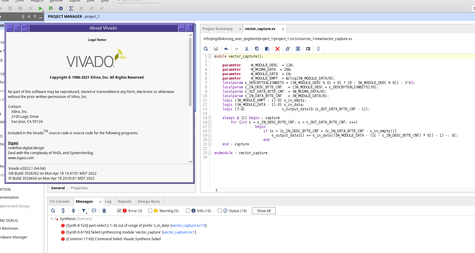

I further test with Vivado v2022.1. I'm also getting the similar synthesis error [Synth 8-524] part-select [-1:-8] out of range of prefix 's_in_data' check image:

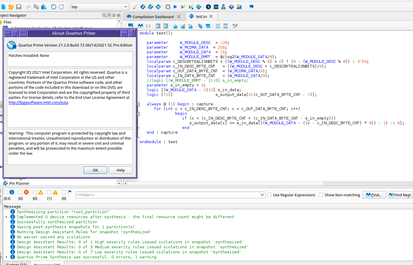

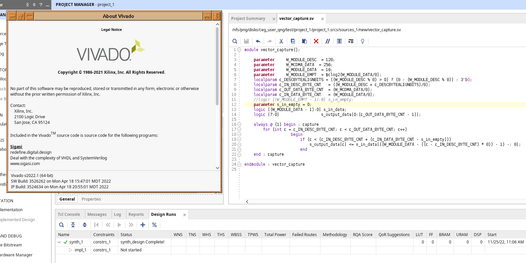

I further found out that the root cause is at variable s_in_empty in module vector_capture.sv. You can't use logic type s_in_empty in for loop if statement. If change the type of variable s_in_empty from logic to for example parameter, both Quartus and Vivado can successfully synthesis the code check image:

Therefore, I believe this is expected behavior.

Thanks,

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Ranesh ,

Let me know if you have any further update or concern.

Thanks,

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

I have noticed that if I eliminate s_in_empty in the if condition, there is no synthesis error. In another segment of my vector_capture.sv I am using an internal counter that is to count number bytes in s_output_data and there is no synthesis error in this line.

I have attached modified vector_capture.sv for your consideration.

Please note that line 142 is commented and 143 is introduced to avoid previous synthesis error.

Also, please note that line 147 to line 153 are introduced with s_outbytecount, but the line 150 if condition is not produce any synthesis error as before.

Regards,

Ranesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

I forgot to mentioned that s_outbyteconut is also a logic type and used in for loop if statement.

Regards,

Ranesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Ranesh ,

In your updated code, there are differences between the lines 144 and 151.

Line 144:

s_output_data[c] <= s_in_data[((W_MODULE_DATA - ((c - c_IN_DESC_BYTE_CNT) * 8)) - 1) -: 8];

Line 151:

s_output_data[d] <= s_in_data[((W_MODULE_DATA - ((d - s_outbytecount) * 8))- 1) -: 8];

For line 151, if change s_outbytecount to c_IN_DESC_BYTE_CNT also produce the error below:

Error(13224): Verilog HDL or VHDL error at vector_capture.sv(151): index 136 is out of range [15:0] for 's_in_data'

For line 144, if change c_IN_DESC_BYTE_CNT to s_in_empty and with previous if (c < (c_IN_DESC_BYTE_CNT + (c_IN_DATA_BYTE_CNT - s_in_empty))), there'll be no error produced as well.

So you're comparing two different things. Let me know if you have any further concern.

Thanks,

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

Please don't compare line 144 and 151, they are not causing this error. If you change line 144 to have

(c - c_IN_DESC_BYTE_CNT) > 2, it will produce negative index for s_in_data and similarly, in line 151, if

(d - s_outbytecount) > 2, it will produce negative index for s_in_data. This is because W_MODULE_DATA = 16.

Please don't change any of these lines.

Please compare lines 142 (commented), 143 with line 150.

If line 142 is used, the compiler produced following error:

Error(13224): Verilog HDL or VHDL error at vector_capture.sv(144): index -8 is out of range [15:0] for 's_in_data'

If line 143 used, which does not use s_in_empty in for loop if statement, the compiler does not produced any error

For this error, you have mentioned:

You can't use logic type s_in_empty in for loop if statement.

Please note that line 150 is using a logic type s_outbytecount in for loop if statement, which does not cause any synthesis error. This shows that a logic type can be used in for loop if statement.

Thank you.

Regards,

Ranesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Ranesh ,

parameter W_MCDMA_DATA = 256,

parameter W_MCDMA_EMPT = $clog2(W_MCDMA_DATA/8),

logic [(W_MCDMA_EMPT - 1):0] s_outbytecount;

Variable s_outbytecount is 5-bit variable. So it should range from 0 to 31 right.

If s_outbytecount is 0 means in line 151 if I change s_outbytecount to number 0, I'm getting the same error as before:

Error(13224): Verilog HDL or VHDL error at vector_capture.sv(151): index -8 is out of range [15:0] for 's_in_data'

If I change s_outbytecount to number 31, I'm also getting error:

Error(13224): Verilog HDL or VHDL error at vector_capture.sv(151): index 256 is out of range [15:0] for 's_in_data'

But there's no error if using logic s_outbytecount. Probably you can't use logic type in both for loop if statement and if block.

Btw, if this is a bug with Quartus, I should be able to compile the code with other synthesis tool. But I'm getting the same synthesis error with Vivado so I believe this is not a bug. Let me know if you manage to get it compiled with other synthesis tool.

Thanks,

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

You cannot change s_outbytecount to 0 only in line 151, you have to change s_outbytecount in line 150 to 0 as well, because line 151 is constrained by line 150.. By changing value of s_outbytecount to 0 only in line 151, you are making logical error and regardless of compiler this would lead to an error.

Please do not play with s_outbytecount in line 151. You can notice that s_outbytecount is calculated in line 146 and 153.

If you want to change s_outbytecount to see line 151 behavior, you have to calculate (d - s_outbytecount) value in line 151.

W_MODULE_DATA = 16,

c_OUT_DATA_BYTE_CNT = 32,

c_IN_DATA_BYTE_CNT = 2 and

Line 148 to152:

148: for (int d = 0; d < c_OUT_DATA_BYTE_CNT; d++)

149: begin

150: if ((d >= s_outbytecount) && (d < (s_outbytecount + c_IN_DATA_BYTE_CNT)))

151: s_output_data[d] <= s_in_data[((W_MODULE_DATA - ((d - s_outbytecount) * 8))- 1) -: 8];

152: end

In line 148 d can take 0 to 31

In line 151 d is constrained to be from s_outbytecount to (s_outbytecount + c_IN_DATA_BYTE_CNT) - 1

Since W_MODULE_DATA = 16, ((d - s_outbytecount) * 8)) can take only 0 or 8.

when ((d - s_outbytecount) * 8)) = 0, ((W_MODULE_DATA - ((d - s_outbytecount) * 8))- 1) = 15

when ((d - s_outbytecount) * 8)) = 8, ((W_MODULE_DATA - ((d - s_outbytecount) * 8))- 1) = 7

So line 151 would not have any errors

In other words, ((d - s_outbytecount) * 8)) cannot be greater than 8 or less than 0.

Please concentrate only on line 142, 143 (these if statements are bound by for loop in line 140)

and 151(this if statement is bound by for loop in line 150).

Regards,

Ranesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

There was a mistake in last line of my last reply:

The lie

"Please concentrate only on line 142, 143 (these if statements are bound by for loop in line 140)

and 151(this if statement is bound by for loop in line 150)."

is not correct. It should be

"Please concentrate only on line 142, 143 (these if statements are bound by for loop in line 140 and 145)

and 150 (this if statement is bound by for loop in line 148 and 152)."

Thank you.

Regards,

Ranesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just an update. Still pending response from internal expert.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Ranesh ,

Internal Feedback:

For the expression if (c < (c_IN_DESC_BYTE_CNT + (c_IN_DATA_BYTE_CNT - s_in_empty)))

1. When "s_in_empty" is of type logic, the expression in if condition can't be evaluated at compile time. So all possible indices are generated for "s_in_data".

e.g., for value of c = 18 onwards, index for s_in_data becomes negative.

Let me further check with expert on the second example you provided.

Thanks,

Best Regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

Please note that the expression if (c < (c_IN_DESC_BYTE_CNT + (c_IN_DATA_BYTE_CNT - s_in_empty))) is bound by the expression for (int c = c_IN_DESC_BYTE_CNT; c < c_OUT_DATA_BYTE_CNT; c++). This limits c not to be below c_IN_DESC_BYTE_CNT, which is 26. So in the expression s_output_data[c] <= s_in_data[((W_MODULE_DATA - ((c - c_IN_DESC_BYTE_CNT) * 8)) - 1) -: 8], which is bound by the expression that you have mentioned, c can only be 26 or 27, because s_in_empty is single bit signal and c_IN_DATA_BYTE_CNT = 2.

I am re-attaching my explanation in word document for you and the expert

Regards,

Ranesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ranesh,

I think it would be helpful if you can provide a stripped code example that shows the problem, without all unneeded project stuff and with irrelevant module instantiations commented out.

Regards

Frank

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

I have attached entire folder for you and the expert.

Thank you.

Ranesh

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page