- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

I'm trying to connect datas and a clock from Cyclone 10 GX(output) to another video device(input).

The video device's pins use 3V power, so I need to set 3.0V these datas and a clock.

I set 3.0V by Pin Planner, and processed fitting stage.

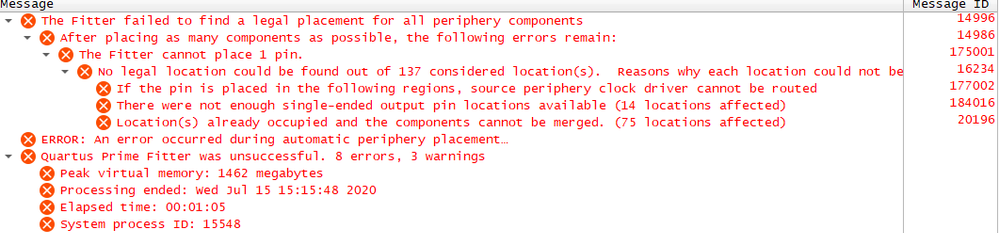

But the error message appeared as attached screen shot.

I used 24 data or control signals and 1 clock as 3.0V, I think 3.0V pins aren't in shortage because the bank 2L(it's the only bank can use 3.0V) have 48 pins.

As a test, I removed I/O standard strict of the clock out pin, compilation passed and pin was assigned 1.8V I/O automatically.

This clock out signal is from following route,

LVDS clock input(from external device) > LVDS SERDES(RX) IP inclock pin > rx_coreclock pin > cclock out pin of Cyclone 10 GX

I found that this clock signal type is Periphery (not Global).

Can I change this to a Global clock, or have any simple way to resolve this problem ?

application version : Quartus Prime Pro 20.1.0 Build 177

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi YFuji17,

It's seem like you not assigned the pin properly.

May I know your Cyclone 10 GX OPN number?

And can you screenshot your pin planner and send it here?

Thanks.

Regards,

Matt

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page