- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

I am new to FPGA and Quartus and just truing to work with it. I am using Quartus Prime Lite edition 22.1. on Win 10.

I write a sample module with 3 always block doing just simple stuff. As counter variables I assign reg[7:0] r_cnt...

but after 3 variables all other reg[] suddenly becomes combinational groups instead of registered like it was before so that u_cnt,b_cnt,l_cnt are regestered group and b_bit become combinational group and all variables that I am creatine going into combinational groups.

How one can fix this issue?

Here is the code:

module controller (

input clk,

input las_en,

input Rx,

output reg las1,

output reg las2,

output reg u_clk

);

reg[15:0] u_cnt;

reg[5:0] b_cnt;

reg[5:0] l_cnt;

reg[7:0] d_bit;

reg l_flg,Rx_flg;

reg[7:0] dat_in;

initial begin u_clk = 0; l_flg = 1;Rx_flg = 0; las1 = 0; b_cnt = 0;bit = 0; dat_in = 0; end

always @(posedge clk) begin // lasers pulse control

if (las_en & l_flg) begin

las1 = 1; las2 = 1;

l_flg = 0;

end

if(l_flg == 0)l_cnt = l_cnt + 1;

if(l_cnt == 25) begin

las1 = 0; las2 = 0;

l_cnt = 0;

l_flg = 1;

end

end

always @(posedge clk) begin // UART clk

if(Rx==0) Rx_flg = 1;

if(Rx_flg) begin

u_cnt = u_cnt+1;

if(u_cnt== 109) begin u_cnt = 0; u_clk = ~u_clk; b_cnt = b_cnt + 1;end

if(b_cnt== 18 ) begin b_cnt = 0; Rx_flg = 0; end

end

end

always @(posedge u_clk) begin

bit = bit + 1;

dat_in[bit] = Rx;

if(bit==10) bit = 0;

end

endmodule

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi FvM,

I am checking status of variables in waveform editor when I am trying to add variable to watch them. And in main code when you are right click on variable -> locate node and if it is registered group you can see menu locate in ... and if it is combinational group - locate node menu are not accessible.

So is it possible to avoid this or fix it? And why first 3 variable are registered and any other not? Declaration and usage are the same.

thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you show some screenshots of what you are seeing?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

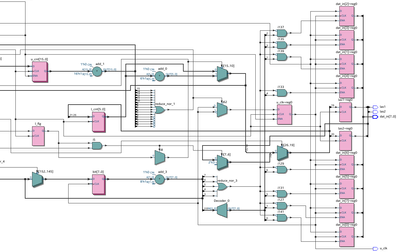

Hi sstrell, here is screenshots and project files.

in Node finder picture you can see that some variables are in Combinational and some in Registered groups. But all variables decaled as reg [].

Even in code by trying to locate node you can see that some variables are recognized and can be selected but not variables that was "converted " in Combinational group.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a problem that some variable names mentioned in your first post can't be found in the code, e.g. b_bit. So it's impossible to see which code details are causing the reported effects. It can be either expectable because the variables have lost their register function or it's just a bug. Personally I'm using classical ModelSim testbenches and GUI for simulation, didn't yet use waveform editor.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi FvM,

you are right I post code with changes.

I post project and pictures of how I was checking variable status.

About ModelSim vs Waveform may be it doesn't matter much because it can be can seen in pictures that when I am trying to locate node from main editor I can locate variable if it is registered and not if it is combinational. So you can easy see variable status even outside of simulation.

I change blocking assignments to unblocking but no effect.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are using bit_cnt as an index for dat_in, but the value of bit_cnt can become greater than 7 (the range you set for dat_in) because you are incrementing it up to 10 at max. So without compiling it myself, something is getting optimized or latched because of this. You probably are seeing warnings in the messages window about this. Can you post those warnings?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

By adding output dat_in,

in the code, you would able to see the reg[7:0] bit and reg[7:0] dat_in check the image below:

Thanks,

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sheng,

Your advice worked very good. It fix problem. Now I can see everything like it was declared. Thanks a lot.

But just for understanding - why regs was converted to combinational?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Those registers are not converted to combinational, but being optimized away because don't have an output so didn't show up.

Thanks,

Best Regards,

Sheng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Let me know if you have any further concern or update on this thread.

Thanks,

Best Regards,

Sheng

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page