- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Cleaning out some code to get a more reusable and family independent code base, I noticed a difference in VHDL2008 support between the standard (20.1) and Pro(20.4) versions of Quartus I am using.

I guess it is not a bug but it appears the Standard version does not support generic types and functions as in the example below, whilst the pro version does not complain.

entity some_block is

generic (

type RECORD_TYPE;

SLV_LENGTH : integer;

function PACK(d_rec: RECORD_TYPE) return std_logic_vector;

function UNPACK(d_slv: std_logic_vector) return RECORD_TYPE;

DEVICE_FAMILY : string;

FIFO_DEPTH : integer

);

port (

arst : in std_logic;

wrclk : in std_logic;

wrreq : in std_logic;

data_in : in RECORD_TYPE;

rdclk : in std_logic;

rdreq : in std_logic;

data_out : out RECORD_TYPE;

empty : out std_logic

);However I do not seem to find an overview of these differences online.

As we work with different FPGAs (eg Cyclone 10 LP and Cyclone 10 GX) which are either bound to the Standard or the Pro version, this seems to imply we cannot use full 2008 support on all are designs and require a separate code base for either toolflow.

Is my observation correct?

If so, is there any way (I did not find yet) to overcome this? eg. allowing this code to be used for eg. a Cyclone 10 LP design?

Thanks in advance for your replies

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi LukasR,

This is because the Quartus Pro version and Standard version are using different synthesis engine under the hood.

In your code compilation using the pro version, does the RTL viewer show the expected behavior result? If yes, then you may check your email.

Thanks.

Best Regards,

Ven Ting

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ven Ting,

Thank you for your reply.

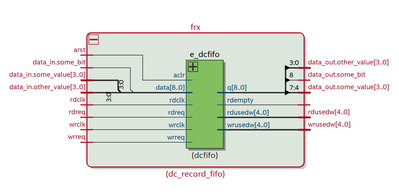

Running the code in the src folder below (demo toplevel) in a Quartus Prime Pro 2020.1 does give the expected RTL-viewer output:

This uses the Cyclone 10 GX as device family, as the Cyclone 10 LP is not supported.

The difference in which engine is used is what I feared for.

Is there any hope for a workaround so this code could also be used to work on FPGAs like the Cyclone 10 LP or other/older Standard version supported FPGAs?

Kind regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Lukas,

Kindly check your email box. I have sent you an email regarding this issue.

Thanks.

Best Regards,

Ven Ting

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m glad that your question has been addressed through email, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best Regards,

Ven Ting

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page