- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm trying to implement a multiplication program using file I/O written in C++ on FPGA using intelhlscompiler.

I have completed the high-level synthesis and implemented it on 5CSXFC6D6F31C6, but the calculation results were not output to file, so I decided to turn on the led at the end of the verilog to test if the circuit is working.

When I tried to place the pins, I got the error Error (171011): Can't assign node "led" to location PIN_AA24 -- node is type Combinational cell.

How can I solve this problem?

Translated with www.DeepL.com/Translator (free version)

---------------------------------------------C++program------------------------------------------

#include "HLS/hls.h"

#include <stdio.h>

using namespace ihc;

component int calc(int a,int b){

return a*b;

}

int main(void)

{

FILE * fp=NULL;

int seisuu=0; // 数字1

int seisuu2=0; // 数字2

int ans=0;

fp = fopen("input.txt", "r");

if(fp == NULL) {

printf("ファイルを開くことが出来ませんでした.¥n");

}while (fscanf(fp, "%d,%d", &seisuu,&seisuu2) != EOF)

{

//printf("%d %d\n", seisuu,seisuu2);

printf("%d*%d=%d",seisuu,seisuu2,calc(seisuu,seisuu2));

}

ans = calc(seisuu,seisuu2);fp = fopen("output.txt", "w");

fprintf(fp,"%d",ans);

fclose(fp);

return 0;

}

----------------------------------------------------------------------------------------------------------

----------------------------------------HLS Generated files--------------------------------------------

module quartus_compile (

input logic resetn

, input logic clock

, input logic [0:0] calc_start

, output logic [0:0] calc_busy

, output logic [0:0] calc_done

, input logic [0:0] calc_stall

, output logic [31:0] calc_returndata

, input logic [31:0] calc_a

, input logic [31:0] calc_b

, output led

);

logic [0:0] calc_start_reg;

logic [0:0] calc_busy_reg;

logic [0:0] calc_done_reg;

logic [0:0] calc_stall_reg;

logic [31:0] calc_returndata_reg;

logic [31:0] calc_a_reg;

logic [31:0] calc_b_reg;

always @(posedge clock) begin

calc_start_reg <= calc_start;

calc_busy <= calc_busy_reg;

calc_done <= calc_done_reg;

calc_stall_reg <= calc_stall;

calc_returndata <= calc_returndata_reg;

calc_a_reg <= calc_a;

calc_b_reg <= calc_b;

end

reg [2:0] sync_resetn;

always @(posedge clock or negedge resetn) begin

if (!resetn) begin

sync_resetn <= 3'b0;

end else begin

sync_resetn <= {sync_resetn[1:0], 1'b1};

end

end

calc calc_inst (

.resetn(sync_resetn[2])

, .clock(clock)

, .start(calc_start_reg)

, .busy(calc_busy_reg)

, .done(calc_done_reg)

, .stall(calc_stall_reg)

, .returndata(calc_returndata_reg)

, .a(calc_a_reg)

, .b(calc_b_reg)

);

endmodule

-----------------------------------------------------------------------------------------------------------

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't know much about HLS, but in your Verilog code, you create led as an output but don't connect it to anything.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

led <= ?

You have to make an assignment to it, just like you make assignments to other signals in the code.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your kindness.

led <= calc_returndata;

and I was able to implement it.

However, the LED did not light up and there was no file output.

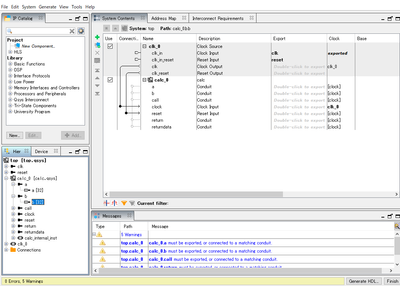

If there is any concern, it is related to qsys. I have the following connection, is it correct?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am presuming that you want returndata in the Platform Designer system to appear on the LED. You need to export the returndata interface (double-click in the Export column and give it a name) and instantiate the system, connecting the exported interface (single signal interface, I presume) to the led output. You can see the instantiation template you'll need in the Generate menu in Platform Designer. You'd need to recompile the design of course.

Again, I don't know how this fits into HLS, but for normal FPGA design, this is what would be required.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @gazel,

Thank you for posting in Intel community forum, hope this message find you well.

Please do let us know if you are still facing the difficulties mention and we would get back to you as soon as possible.

Best Wishes

BB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @gazel,

Good day, as we do not receive any further clarification on what is provided, we would assume challenge are resolved. Hence thread will no longer monitor this thread. For new queries, please feel free to open a new thread and we will be right with you. Pleasure having you here.

Best Wishes

BB

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page