- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

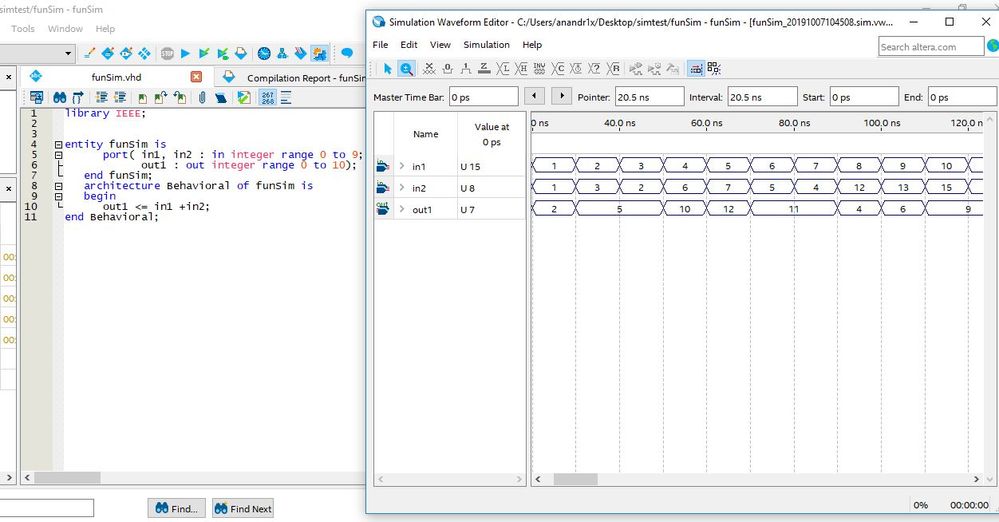

Hello, I'm trying to perform functional simulation using the simulation waveform editor of quartus prime lite edition, that uses Modelsim-altera.

I tried a very basic circuit design with 2 inputs and one output of type integer , but I've got an error "Fatal: (vsim-3807) Types do not match between component and entity" Modelsim is unable to load the design.

My question is , is it possible to perform the functional simulation using integer type ports ?

Thanks

Regards

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sara,

is it possible to perform the functional simulation using integer type ports?

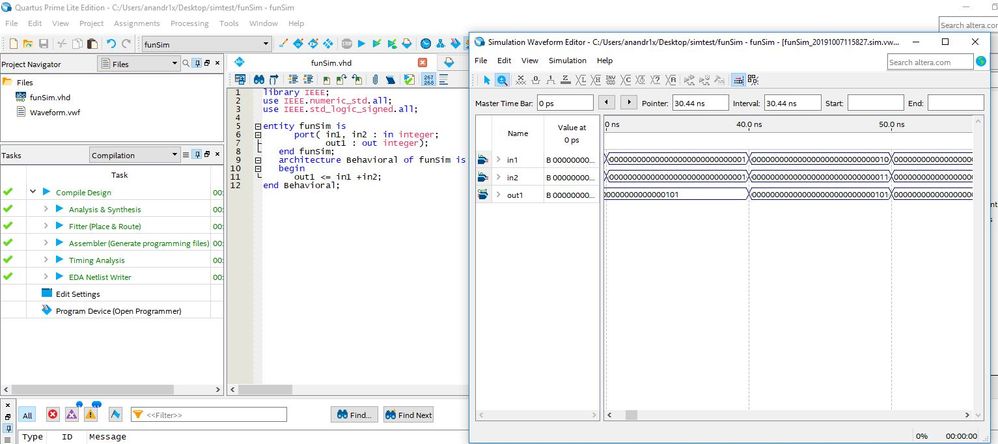

>>Yes, Run full compilation. with libraries

use IEEE.numeric_std.all;

use IEEE.std_logic_signed.all;

The fatal error is related to the type mismatch or libraries used.

We can specify the range of values that an object of type integer is going to have.

Limiting the range reduces the FPGA resources needed to implement the design. Moreover, it gives us a means of checking for errors in the early stages of the design or simulation.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Anand for your reply .

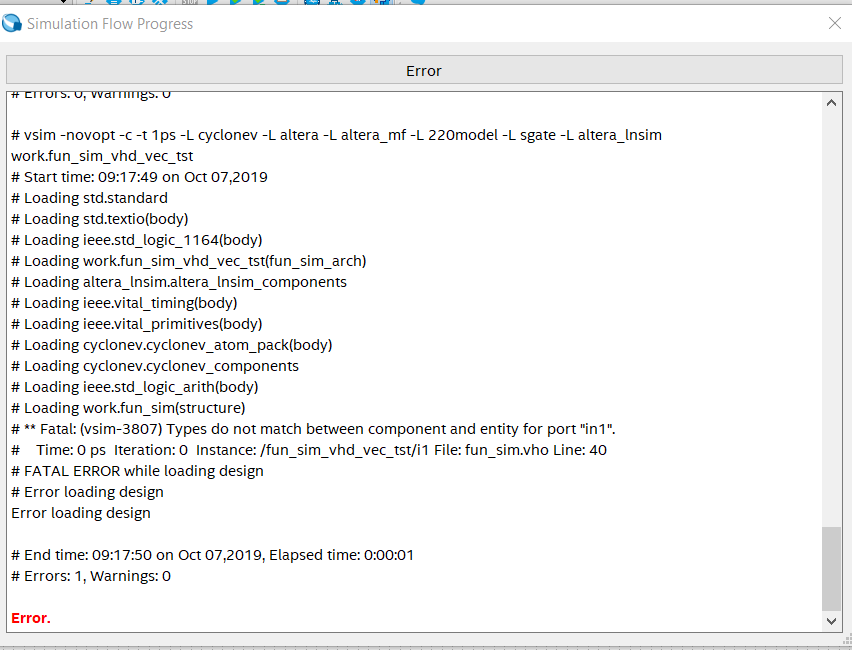

I reproduced the same VHDL codes you provided but i still get the same error.

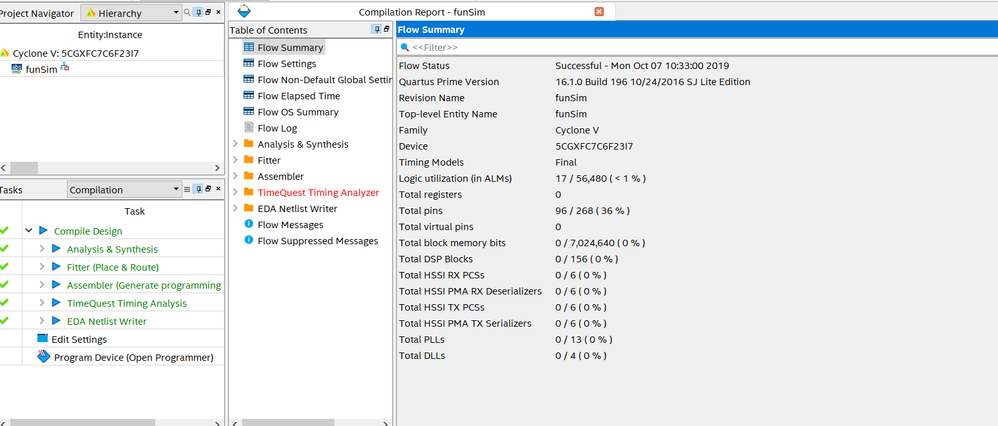

I attached figures to show you the problem

I have another question. since the integer range is from 0 to 9 , why in the simulation it goes from 0 to 15 ?

Looking forward to reading from you.

Thank you before hand

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Determining the location of the ModelSim executable...

Using: C:\intelFPGA_lite\16.1\modelsim_ase\win32aloem

To specify a ModelSim executable directory, select: Tools -> Options -> EDA Tool Options

Note: if both ModelSim-Altera and ModelSim executables are available, ModelSim-Altera will be used.

**** Generating the ModelSim Testbench ****

quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off fun_sim -c fun_sim --vector_source="D:/My_FPGA_projects/fun_sim/Waveform.vwf" --testbench_file="D:/My_FPGA_projects/fun_sim/simulation/qsim/Waveform.vwf.vht"

Info: *******************************************************************

Info: Running Quartus Prime EDA Netlist Writer

Info: Version 16.1.0 Build 196 10/24/2016 SJ Lite Edition

Info: Copyright (C) 2016 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and its AMPP partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel MegaCore Function License Agreement, or other

Info: applicable license agreement, including, without limitation,

Info: that your use is for the sole purpose of programming logic

Info: devices manufactured by Intel and sold by Intel or its

Info: authorized distributors. Please refer to the applicable

Info: agreement for further details.

Info: Processing started: Mon Oct 07 09:23:29 2019

Info: Command: quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off fun_sim -c fun_sim --vector_source=D:/My_FPGA_projects/fun_sim/Waveform.vwf --testbench_file=D:/My_FPGA_projects/fun_sim/simulation/qsim/Waveform.vwf.vht

Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.

Completed successfully.

**** Generating the functional simulation netlist ****

quartus_eda --write_settings_files=off --simulation --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory="D:/My_FPGA_projects/fun_sim/simulation/qsim/" fun_sim -c fun_sim

Info: *******************************************************************

Info: Running Quartus Prime EDA Netlist Writer

Info: Version 16.1.0 Build 196 10/24/2016 SJ Lite Edition

Info: Copyright (C) 2016 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and its AMPP partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel MegaCore Function License Agreement, or other

Info: applicable license agreement, including, without limitation,

Info: that your use is for the sole purpose of programming logic

Info: devices manufactured by Intel and sold by Intel or its

Info: authorized distributors. Please refer to the applicable

Info: agreement for further details.

Info: Processing started: Mon Oct 07 09:23:31 2019

Info: Command: quartus_eda --write_settings_files=off --simulation=on --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory=D:/My_FPGA_projects/fun_sim/simulation/qsim/ fun_sim -c fun_sim

Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.

Info (204019): Generated file fun_sim.vho in folder "D:/My_FPGA_projects/fun_sim/simulation/qsim//" for EDA simulation tool

Info: Quartus Prime EDA Netlist Writer was successful. 0 errors, 1 warning

Info: Peak virtual memory: 4721 megabytes

Info: Processing ended: Mon Oct 07 09:23:32 2019

Info: Elapsed time: 00:00:01

Info: Total CPU time (on all processors): 00:00:01

Completed successfully.

**** Generating the ModelSim .do script ****

D:/My_FPGA_projects/fun_sim/simulation/qsim/fun_sim.do generated.

Completed successfully.

**** Running the ModelSim simulation ****

C:/intelFPGA_lite/16.1/modelsim_ase/win32aloem/vsim -c -do fun_sim.do

Reading C:/intelFPGA_lite/16.1/modelsim_ase/tcl/vsim/pref.tcl

# 10.5b

# do fun_sim.do

# ** Warning: (vlib-34) Library already exists at "work".

# Model Technology ModelSim - Intel FPGA Edition vcom 10.5b Compiler 2016.10 Oct 5 2016

# Start time: 09:23:33 on Oct 07,2019

# vcom -work work fun_sim.vho

# -- Loading package STANDARD

# -- Loading package TEXTIO

# -- Loading package std_logic_1164

# -- Loading package altera_lnsim_components

# -- Loading package VITAL_Timing

# -- Loading package VITAL_Primitives

# -- Loading package cyclonev_atom_pack

# -- Loading package cyclonev_components

# -- Loading package std_logic_arith

# -- Compiling entity fun_sim

# -- Compiling architecture structure of fun_sim

# End time: 09:23:33 on Oct 07,2019, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

# Model Technology ModelSim - Intel FPGA Edition vcom 10.5b Compiler 2016.10 Oct 5 2016

# Start time: 09:23:33 on Oct 07,2019

# vcom -work work Waveform.vwf.vht

# -- Loading package STANDARD

# -- Loading package TEXTIO

# -- Loading package std_logic_1164

# -- Compiling entity fun_sim_vhd_vec_tst

# -- Compiling architecture fun_sim_arch of fun_sim_vhd_vec_tst

# End time: 09:23:34 on Oct 07,2019, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -novopt -c -t 1ps -L cyclonev -L altera -L altera_mf -L 220model -L sgate -L altera_lnsim work.fun_sim_vhd_vec_tst

# Start time: 09:23:34 on Oct 07,2019

# Loading std.standard

# Loading std.textio(body)

# Loading ieee.std_logic_1164(body)

# Loading work.fun_sim_vhd_vec_tst(fun_sim_arch)

# Loading altera_lnsim.altera_lnsim_components

# Loading ieee.vital_timing(body)

# Loading ieee.vital_primitives(body)

# Loading cyclonev.cyclonev_atom_pack(body)

# Loading cyclonev.cyclonev_components

# Loading ieee.std_logic_arith(body)

# Loading work.fun_sim(structure)

# ** Fatal: (vsim-3807) Types do not match between component and entity for port "in1".

# Time: 0 ps Iteration: 0 Instance: /fun_sim_vhd_vec_tst/i1 File: fun_sim.vho Line: 40

# FATAL ERROR while loading design

# Error loading design

Error loading design

# End time: 09:23:34 on Oct 07,2019, Elapsed time: 0:00:00

# Errors: 1, Warnings: 0

Error.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you ran full Quartus Compilation?

You should not see that error after full compilation

Attached project

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi , I compiled your project successfully , but i'm having the same error at simulation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

the simulation report is :

Determining the location of the ModelSim executable...

Using: C:\intelFPGA_lite\16.1\modelsim_ase\win32aloem

To specify a ModelSim executable directory, select: Tools -> Options -> EDA Tool Options

Note: if both ModelSim-Altera and ModelSim executables are available, ModelSim-Altera will be used.

**** Generating the ModelSim Testbench ****

quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off funSim -c funSim --vector_source="D:/Downloads/simtest/simtest/Waveform.vwf" --testbench_file="D:/Downloads/simtest/simtest/simulation/qsim/Waveform.vwf.vht"

Info: *******************************************************************

Info: Running Quartus Prime EDA Netlist Writer

Info: Version 16.1.0 Build 196 10/24/2016 SJ Lite Edition

Info: Copyright (C) 2016 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and its AMPP partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel MegaCore Function License Agreement, or other

Info: applicable license agreement, including, without limitation,

Info: that your use is for the sole purpose of programming logic

Info: devices manufactured by Intel and sold by Intel or its

Info: authorized distributors. Please refer to the applicable

Info: agreement for further details.

Info: Processing started: Mon Oct 07 10:36:51 2019

Info: Command: quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off funSim -c funSim --vector_source=D:/Downloads/simtest/simtest/Waveform.vwf --testbench_file=D:/Downloads/simtest/simtest/simulation/qsim/Waveform.vwf.vht

utput pin "out1[6]" in vector source file when writing test bench files

Completed successfully.

**** Generating the functional simulation netlist ****

quartus_eda --write_settings_files=off --simulation --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory="D:/Downloads/simtest/simtest/simulation/qsim/" funSim -c funSim

Info: *******************************************************************

Info: Running Quartus Prime EDA Netlist Writer

Info: Version 16.1.0 Build 196 10/24/2016 SJ Lite Edition

Info: Copyright (C) 2016 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and its AMPP partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel MegaCore Function License Agreement, or other

Info: applicable license agreement, including, without limitation,

Info: that your use is for the sole purpose of programming logic

Info: devices manufactured by Intel and sold by Intel or its

Info: authorized distributors. Please refer to the applicable

Info: agreement for further details.

Info: Processing started: Mon Oct 07 10:36:53 2019

Info: Command: quartus_eda --write_settings_files=off --simulation=on --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory=D:/Downloads/simtest/simtest/simulation/qsim/ funSim -c funSim

Info (204019): Generated file funSim.vho in folder "D:/Downloads/simtest/simtest/simulation/qsim//" for EDA simulation tool

Info: Quartus Prime EDA Netlist Writer was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 4723 megabytes

Info: Processing ended: Mon Oct 07 10:36:55 2019

Info: Elapsed time: 00:00:02

Info: Total CPU time (on all processors): 00:00:02

Completed successfully.

**** Generating the ModelSim .do script ****

D:/Downloads/simtest/simtest/simulation/qsim/funSim.do generated.

Completed successfully.

**** Running the ModelSim simulation ****

C:/intelFPGA_lite/16.1/modelsim_ase/win32aloem/vsim -c -do funSim.do

Reading C:/intelFPGA_lite/16.1/modelsim_ase/tcl/vsim/pref.tcl

# 10.5b

# do funSim.do

# ** Warning: (vlib-34) Library already exists at "work".

# Model Technology ModelSim - Intel FPGA Edition vcom 10.5b Compiler 2016.10 Oct 5 2016

# Start time: 10:36:56 on Oct 07,2019

# vcom -work work funSim.vho

# -- Loading package STANDARD

# -- Loading package TEXTIO

# -- Loading package std_logic_1164

# -- Loading package altera_lnsim_components

# -- Loading package VITAL_Timing

# -- Loading package VITAL_Primitives

# -- Loading package cyclonev_atom_pack

# -- Loading package cyclonev_components

# -- Loading package std_logic_arith

# -- Compiling entity funSim

# -- Compiling architecture structure of funSim

# End time: 10:36:57 on Oct 07,2019, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# Model Technology ModelSim - Intel FPGA Edition vcom 10.5b Compiler 2016.10 Oct 5 2016

# Start time: 10:36:57 on Oct 07,2019

# vcom -work work Waveform.vwf.vht

# -- Loading package STANDARD

# -- Loading package TEXTIO

# -- Loading package std_logic_1164

# -- Compiling entity funSim_vhd_vec_tst

# -- Compiling architecture funSim_arch of funSim_vhd_vec_tst

# End time: 10:36:57 on Oct 07,2019, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

# vsim -novopt -c -t 1ps -L cyclonev -L altera -L altera_mf -L 220model -L sgate -L altera_lnsim work.funSim_vhd_vec_tst

# Start time: 10:36:57 on Oct 07,2019

# Loading std.standard

# Loading std.textio(body)

# Loading ieee.std_logic_1164(body)

# Loading work.funsim_vhd_vec_tst(funsim_arch)

# Loading altera_lnsim.altera_lnsim_components

# Loading ieee.vital_timing(body)

# Loading ieee.vital_primitives(body)

# Loading cyclonev.cyclonev_atom_pack(body)

# Loading cyclonev.cyclonev_components

# Loading ieee.std_logic_arith(body)

# Loading work.funsim(structure)

# ** Fatal: (vsim-3807) Types do not match between component and entity for port "in1".

# Time: 0 ps Iteration: 0 Instance: /funsim_vhd_vec_tst/i1 File: funSim.vho Line: 40

# FATAL ERROR while loading design

# Error loading design

Error loading design

# End time: 10:36:57 on Oct 07,2019, Elapsed time: 0:00:00

# Errors: 1, Warnings: 0

Error.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- recreate the project and check

- If facing the same issue again use Quartus 18.1 lite.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

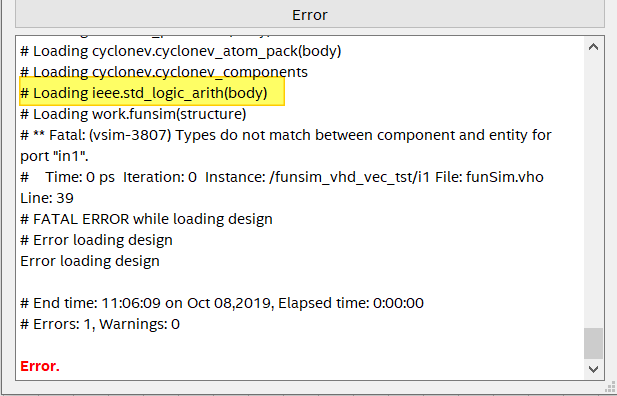

Hello Anand,

I installed quartus prime 18.1 and modelsim .

But the problem is still persistant! i dont understand why. Could you please tell me the procedure you followed to perform you simulation

Though i followed the Altera tutorial for functional simulation, may be i'm missing some part

I noticed that in the error report , that simulator calls the library ieee.std_logic_arith while this one is not declared in your design ? is this normal ?

regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sara,

Try by creating a new project instead of using the same project.

- Created a simple project with an integer as the port type.

- Run analysis & synthesis.

- Created a university program vwf with stimulus and saved the file.

- run full compilation

- double click on .vwf and chick on run functional simulation.

If the issue persists try to use modelsim directly.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anand, Thank you so much for all the support . I really appreciate it . I will try with modelsim

Best regards

Sara

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sara,

Have you solved the issue? Tyr

- Delete db, incremental_db and simulation folder from the project directory.

- Run a full compilation of Quartus project.

- Include the numeric library.

Regards

Anand

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page