- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

I am currently using DSP Builder standard blockset for Startix V development and my development environment is as follows.

- OS: Windows 10 64bit

- Quartus prime standard v18.1 (incluidng DSP builder)

- Matlab R2013a 64bit

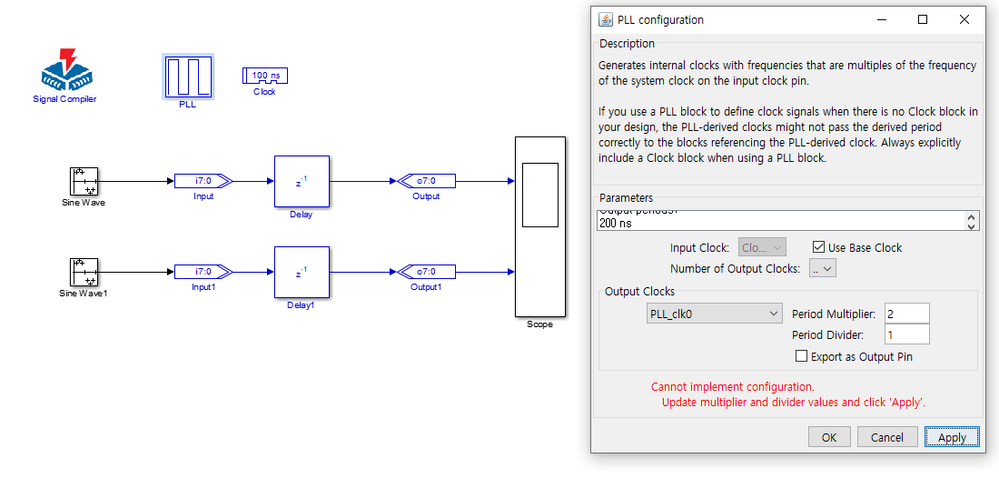

When I using pll block of dsp builder standard blockset in simulink, the following error is displayed. (This is simple model for PLL block testing)

when I modify period multipiler or period divider or number of output clocks in the PLL configuration window,

If you click the Apply button after changing the value, the following error message is displayed.

"Cannot implement configuration. Update multiplier and divider values and tick 'apply' "

Is there any idea how to solve of that Erorr?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Do you have pll block instantiated in your design? The clock parameters should be defined in PLL block generated by platform designer.

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We do not receive any response from you to the previous question/reply/answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

regards,

Farabi

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page