- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

During migration from Quartus 19.1 to 19.4, I recompile project and fitter error appear.

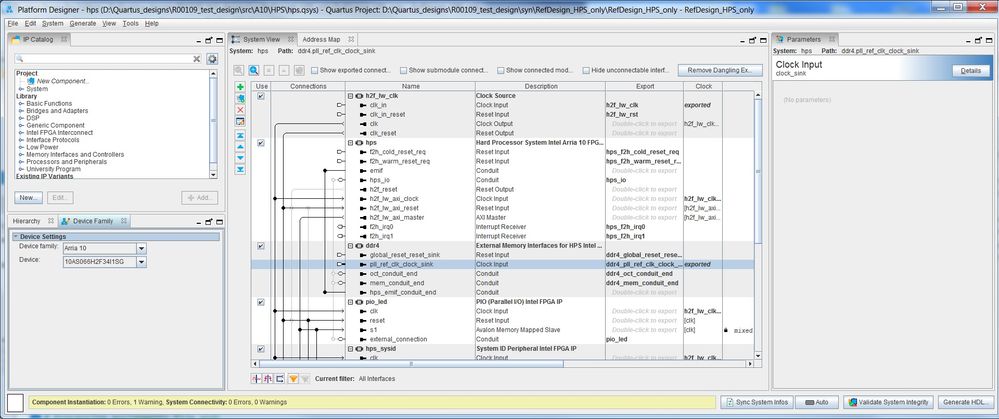

A clock pin assignment conflict is raising between HPS_IOPLL_REFCLK_PIN and hps_ddr4_pll_ref_clk which is directly connected to pll_ref_clk_clock_sink to drive DDR4 (as describe on screenshot of PlatformDesigner)

Quartus fitter indicates folliwing error :

Error (14566): The Fitter cannot place 1 periphery component(s) due to conflicts with existing constraints (1 pin(s)). Fix the errors described in the submessages, and then rerun the Fitter. The Intel FPGA Knowledge Database may also contain articles with information on how to resolve this periphery placement failure. Review the errors and then visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.

Error (175020): The Fitter cannot place logic pin in region (78, 142) to (78, 143), to which it is constrained, because there are no valid locations in the region for logic of this type.

Info (14596): Information about the failing component(s):

Info (175028): The pin name(s): hps_ddr4_pll_ref_clk

Error (16234): No legal location could be found out of 1 considered location(s). Reasons why each location could not be used are summarized below:

Error (175005): Could not find a location with: HPS_IOPLL_REFCLK_PIN (1 location affected)

Info (175029): AL27

Info (175015): The I/O pad hps_ddr4_pll_ref_clk is constrained to the location PIN_AL27 due to: User Location Constraints (PIN_AL27)

Info (14709): The constrained I/O pad is contained within this pin

Error (15307): Cannot apply project assignments to the design due to illegal or conflicting assignments. Refer to the other messages for corrective action.

How can I solve this error (maybe to connect both clock together ?)

Thx,

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please try the following:

- You will need below INIs variable :

- emif_restrict_hps_refclk_to_ac_tile=off

1. Open the fitter_error.qar file, add the INI file with emif_restrict_hps_refclk_to_ac_tile = off.

2. Then re-check the fitter.

Could you please try using these INIs and let us now if the error disappears when placing an HPS-EMIF?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know which device you are working on? Arria 10 SoC Stratix 10 SoC?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi el.ign,

Thank for the help.

The project is for an Arria 10.

I have follow your instructions. I have created an INI file (quartus.ini) and I have added it to project via Settings dialog box.

In this file I paste your instruction, and I rerun the entire compilation project.

Unfortunately, the same error is raising during compilation.

Could you confirm the correct implementation of this option ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I solve my problem today by updating the quartus2.ini file which is on C:\User folder.

I add previous option on it, and compilation is done without any error.

Thank for help,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For clarification, by adding previous option, are you using the INI variable that I provided in my previous reply?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, I added emif_restrict_hps_refclk_to_ac_tile=off variable into quartus2.ini file (in [General 19.4_pro] section) as describe in my previous post.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Noted that and glad that it fixed your issue, feel free to post a new question if you have any.

Best Regards.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page