- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

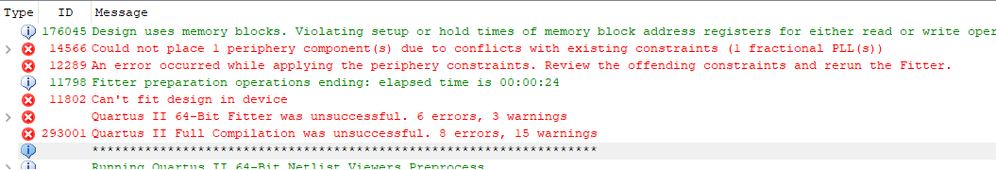

I got an error 14566 : Could not place 1 periphery component(s) due to conflicts with existing constraint (1 fractional PLL(s)).

How can i fix it?

Thanks.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Without knowing anything about the design or even the target device, it's not really possible to diagnose this. Can you provide more details or post the project?

You can also expand the error message to see exactly what the conflict is.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also, if possible share your design which will be ease our job of replicating the scenario.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @PKhan8 ,

Check clk_50 pin assignments.

Clock pin should be AF14/AA16/Y26/K14.

After changing the clock pin, I can run fitter successfully.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page