- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

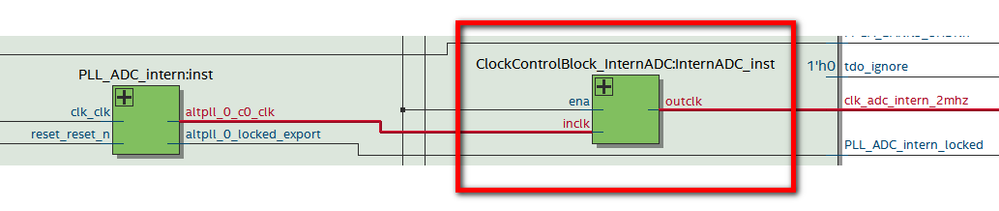

When using the PLL_ADC_internal followed by a ClockControlBlock which goes to the internal Dual-ADC from the Max10, it is not possible to connect it as shown below.

If so, Quartus can't fit it. Now, when this ClockControlBlock is deleted it works. The reason for this Clock-ControlBlock is to disable the PLL_ADC when not used.

Question:

- How would you enable/disable such ADC PLL Clock?

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Put the PLL in reset. Given you don't appear to use the clock out of the PLL for anything else I can't see this being a problem.

Gating a clock to an internal block (internal ADC) may well be something the MAX10 routing cannot accommodate. If this was to an external pin I wouldn't anticipate a problem.

Cheers,

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The disadavantage of a reset is, that it takes much longer until the PLL is working again. Therefore I would like to use a ClockControl. Is this configuration simply not possible??

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If Quartus says 'no' then I suspect it's not possible, although I am a little surprised. I may well try this later...

If you can feed the clock off the device and back in on another pin I'm suspect you'll be able to realise a solution.

Cheers,

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

for whatever reason I can't use the Clock-Controlblock in between the PLL and the Max10 ADC I will try to use the 'reset' of the PLL as you mentioned. Do you know how to assign

for example PLL1 with FPGA clock input CLK1?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page