- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi! I'm trying to transmit data from one FPGA to another (DE1-SoC Cyclone V boards).

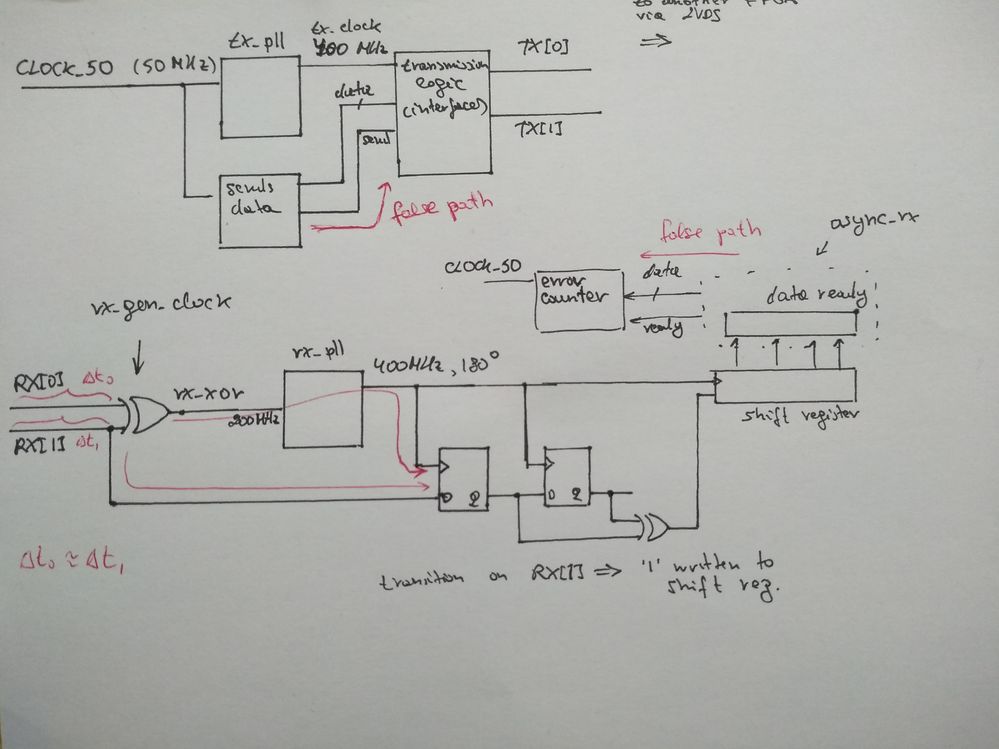

The method I'm using is to have two wires, such that a transition on one wire means that a 0 is transmitted, and a transition on another wire means a 1 is transmitted.

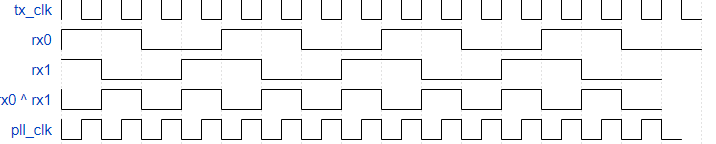

Now by passing this 2 wires through an XOR gate I can essentially generate a clock (200 MHz) (so data is transferred at both rising and falling edge of that clock).

Then I feed that generated clock into a PLL that doubles the frequency (400 MHz) and phase shift it (180 dg) so I can sample the rx0 and rx1 wires to see which one transitioned so I can put a 0 or a 1 in my shift register.

The problem is when I check the path timing, from rx0 port to XOR gate is around 8 ns, and for rx1 to XOR is around 6 ns, how do I constrain them to be the same delay? And from rx0 and rx1 to the registers that samples those the delay also must be the same.

I tried set_min/max_delay, net_delay etc. in SDC, but they seem to be ignored.

Thank you!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you post your .sdc? Also make sure that your .sdc file has been added to the Timing Analysis settings. Those are huge delays so something's fishy with either your constraints or your design.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Thank you for the reply.

Here is my SDC file:

create_clock -name input_clock -period 20.000 [get_ports {CLOCK_50}]

create_clock -name rx_xor -period 4.0 [get_pins {rx_gen_clock|combout}]

derive_pll_clocks

set_false_path -from [get_clocks {input_clock}] -to [get_clocks {u_tx_pll|tx_pll_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk u_tx_pll|tx_pll_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0]}]

set_false_path -from [get_registers *async_rx*] -to [get_registers *error_counter*]

set_net_delay -from [get_registers *async_rx*] -to [get_registers *error_counter*] -max -get_value_from_clock_period dst_clock_period -value_multiplier 0.8

set_max_delay -from [get_ports {RX[0] RX[1]}] -to [get_pins {rx_gen_clock|combout}] 8

set_min_delay -from [get_ports {RX[0] RX[1]}] -to [get_pins {rx_gen_clock|combout}] 7.5Report data path:

report_path -from [get_ports {RX[1] RX[0]}] -to [get_pins {rx_gen_clock|combout}] -npaths 100 -panel_name {Report Path} -multi_corner

Delay From To

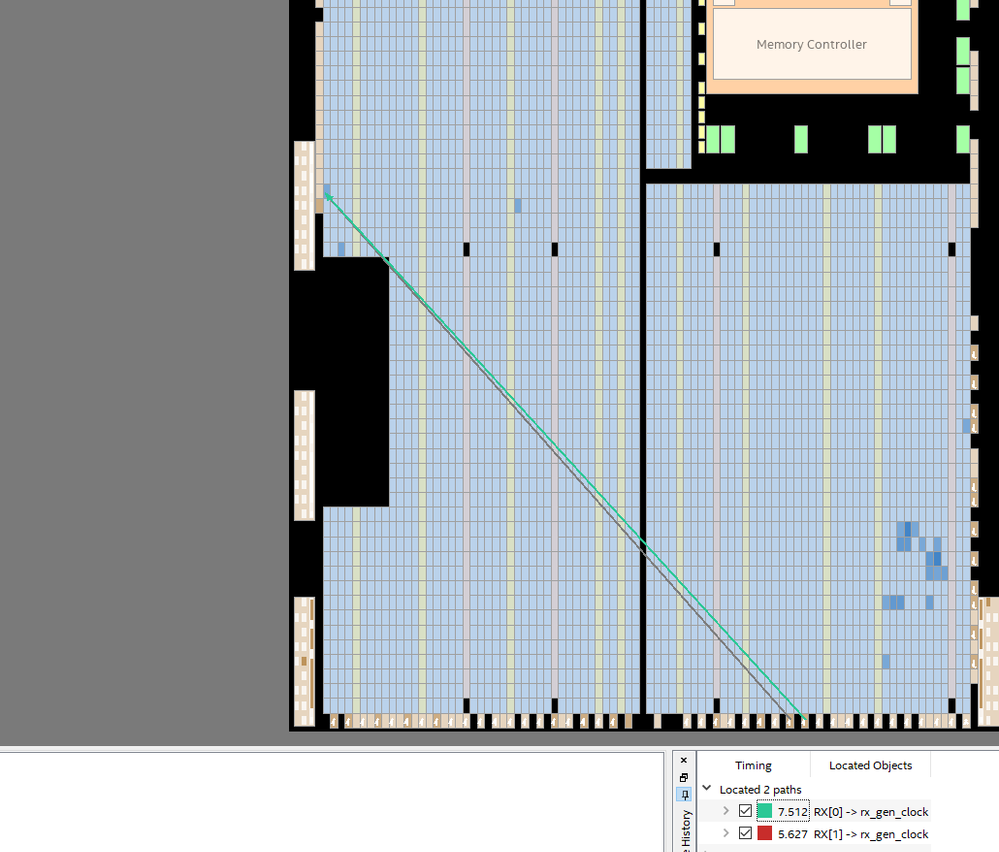

7.512 RX[0] rx_gen_clock|combout

5.627 RX[1] rx_gen_clock|comboutAnd the paths in chip planner:

That essentially what I want to do (I could make the tx_pll clock 200 Mhz by using ddo registers for the outputs)

Btw, I have synthesized it once and it kinda worked, so I could transmit data at 400 Mbps between two FPGAs (sending just an incrementing counter and checking on the other side that I got the right value),

but it's too unreliable especially if I slightly change the code then everything changes. Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vladislav

Thanks for your inquiry and sharing of your design constraint. Let me take a look and get back to you.

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vladislav,

Have you tried set_max_skew?

You may check the syntax herehttps://www.intel.com/content/www/us/en/programmable/quartushelp/current/index.htm#tafs/tafs/tcl_pkg_sdc_ext_ver_1.0_cmd_set_max_skew.htm

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vladislav,

We do not receive any response from you to the previous question/reply/answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page