- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

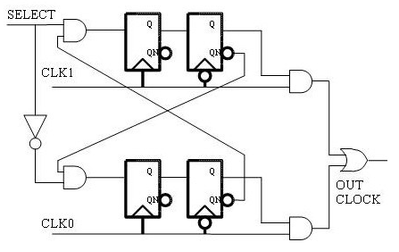

I get an ASIC design which contains many glitch free clock switch as follows picture. When I use auto gated clock conversion option, tool said that it's an unsupported cascaded clock so that tool can't convert it.

Could someone have the experience to share with me? Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KFC,

Can you refer to below document. Make sure all the requirement are met in order to convert gated clock.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Whether someone has the experience to share please? Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KFc,

What device are you using for ASIC prototyping?

Auto Gated Clock Conversion logic option only available Arria series, Cyclone II, Cyclone III, Cyclone IV, HardCopy series, Stratix II, Stratix II GX, Stratix III, Stratix IV, and Stratix V) families. You need to double check this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SyafieqS_Intel

Thank you, SyafieqS_Intel, very much. I'm using Stratix IV. But tool said that it's an unsupported cascaded clock so that tool can't convert it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KFC,

Can you refer to below document. Make sure all the requirement are met in order to convert gated clock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page