- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

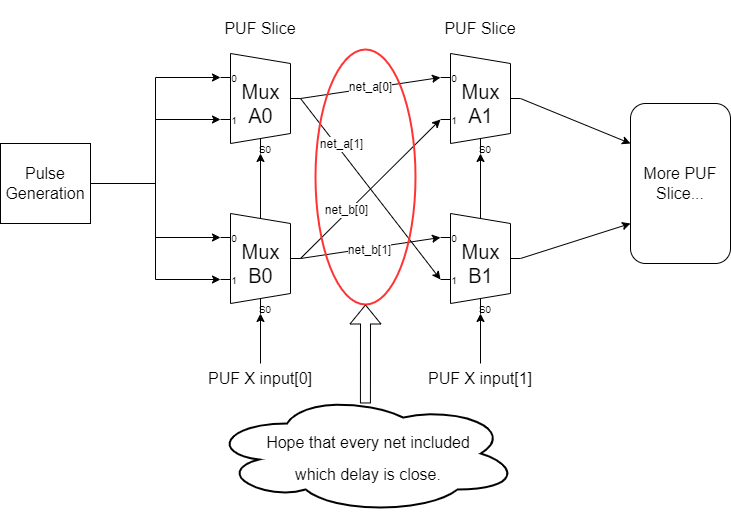

I need to implement a arbiter puf in cycloneive fpga, with the requirement of extreamly net delay parameter about less than 100ps.

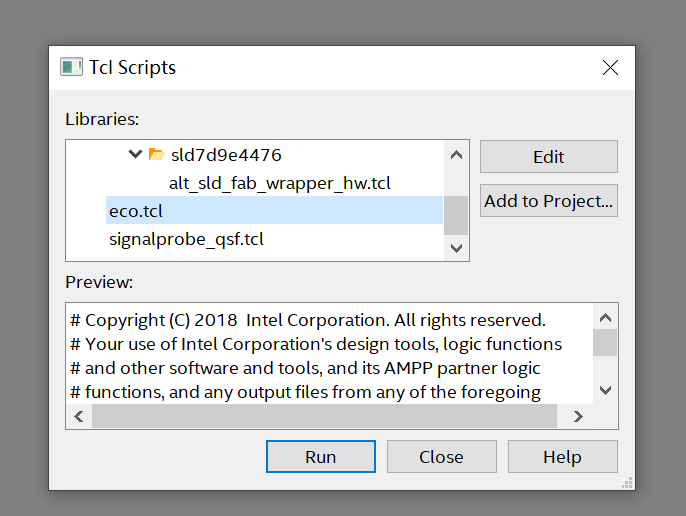

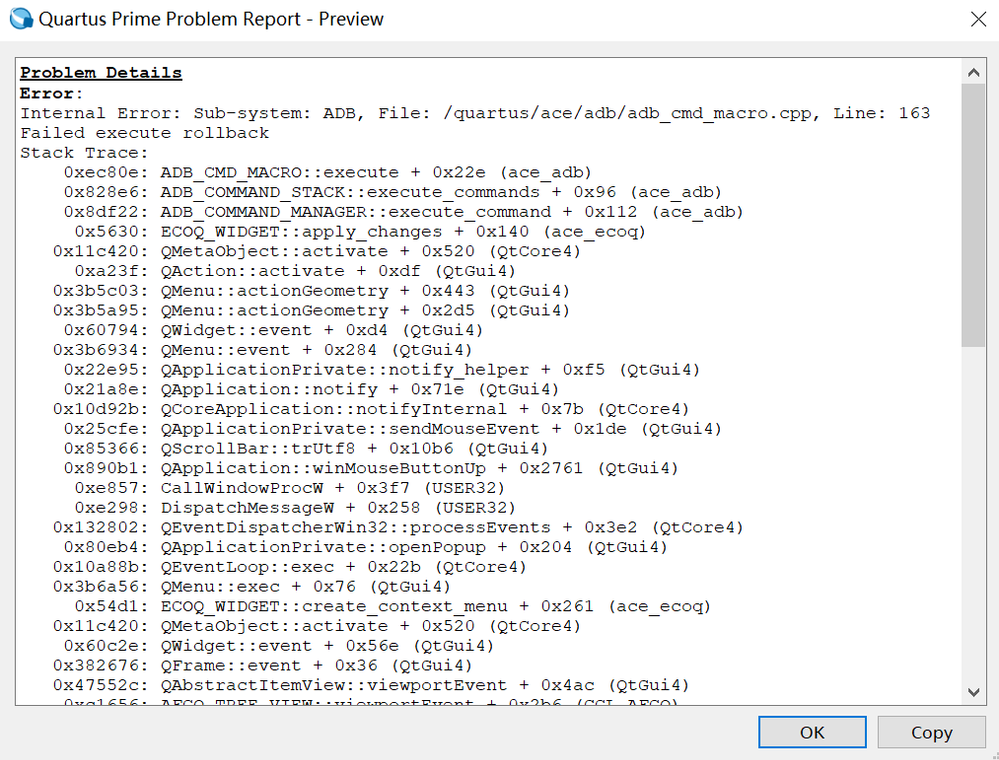

I know that chip planner can change the lut input port in gui display, but I want to fix the lut4 input port in rtl code or any tcl script because of there are many mux implemented by lut4 in my design, using gui is very unefficient.

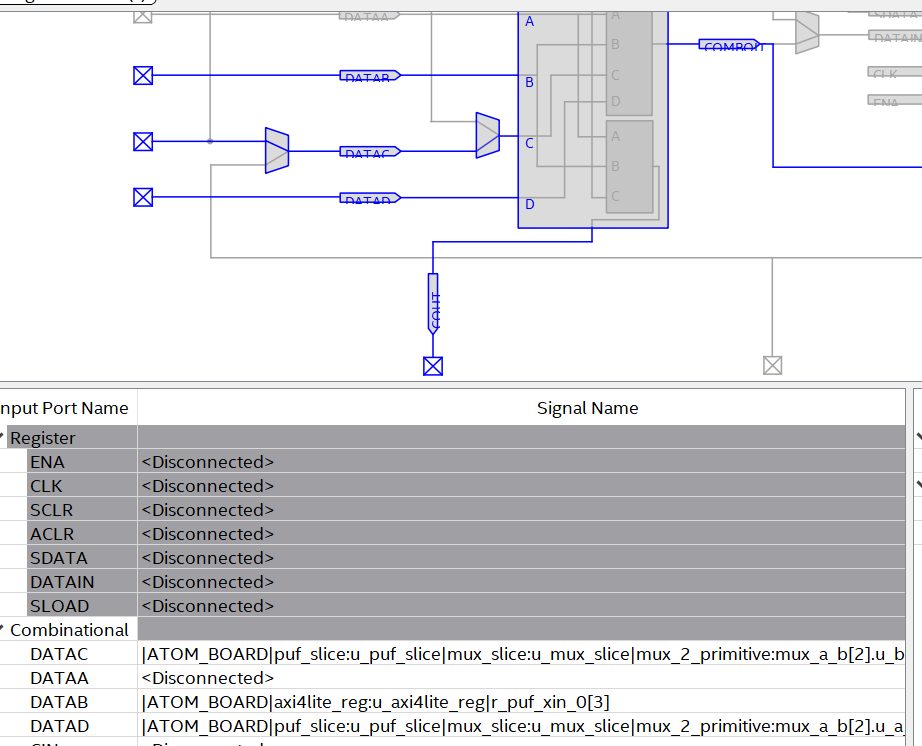

I have tried to use WYSIWYG LCELLS in rtl code like this,but after fitting, the lut4 input ports changed:

-----

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you better explain what you're trying to accomplish here? What is an "arbiter puf"? You should be looking at your HDL code and timing constraints, not trying to make low-level post-fit changes.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Alternatively, you should be looking at timing constraint e.g set_net_delay. Use the set_net_delay command to query the net delays

and perform minimum or maximum timing analysis across nets of <0.1ns

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks a lot SyafieqS!

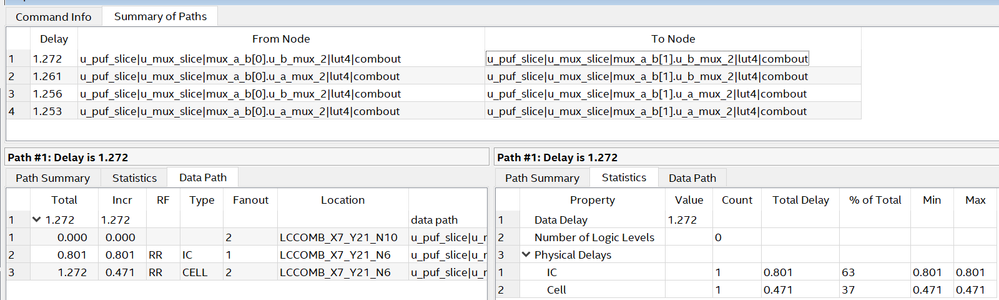

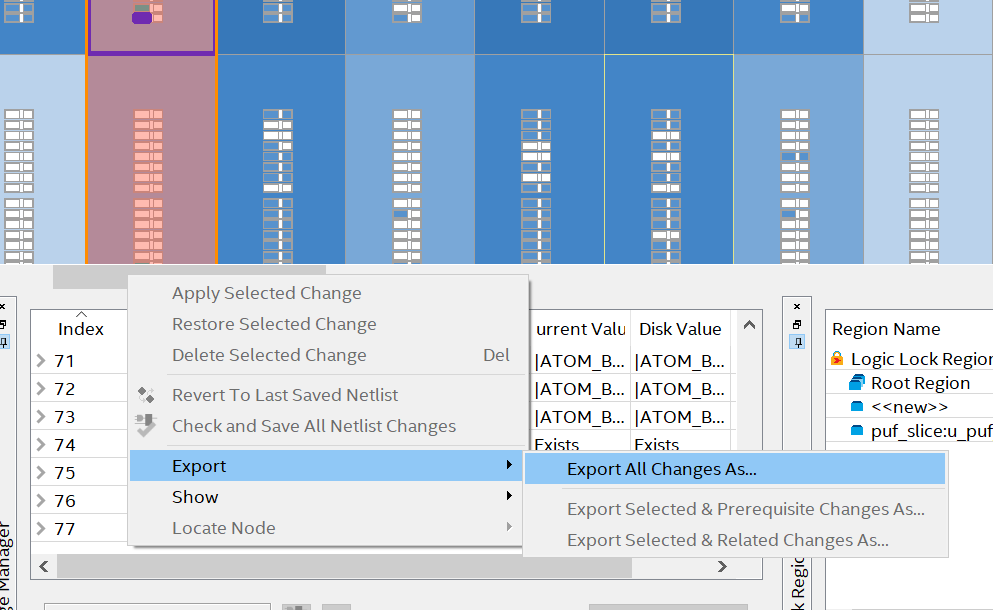

I tried to lock my design LUT location by 'set_location_assignment' for identical net delay between every PUF mux slice.

The 'set_net_delay' constraint works after I delete the constraint of LUT location, let Quartus fit according to the timing constraint.

Now the net delay between PUF mux slice is very close and achieve my goal.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Huang,

Glad you able to resolve it. Let me know if there is any update or any other concern.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page