- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am platform designer, not so familiar with timing.

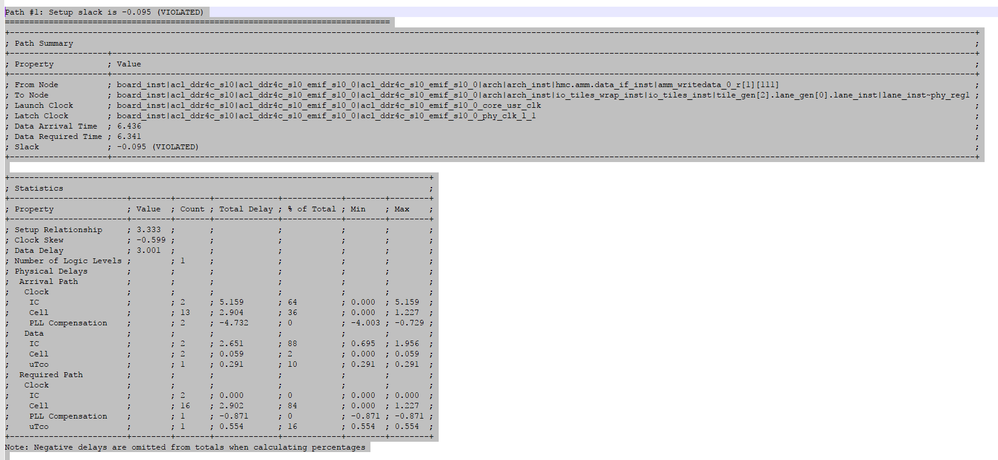

I use QSYS to have a FPGA design, however, I always have some timing violation between DDR core clock and phy clock.

but I can't add pipeline bridge between them, because it's all EMIFIP generated logic.

Can anyone give me a hint?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @dlim thanks for answer

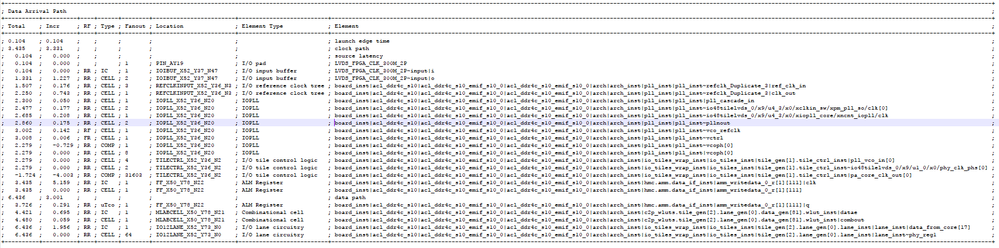

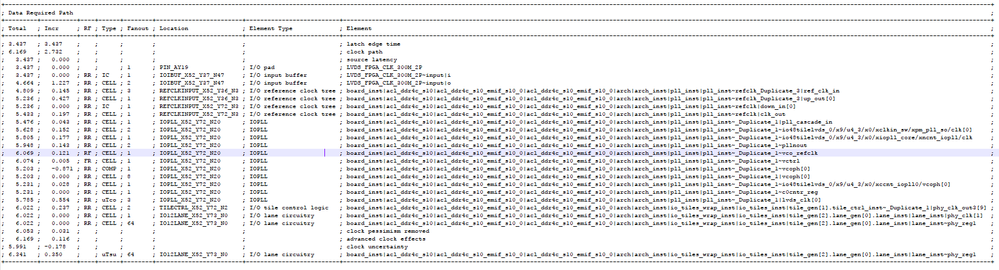

I have check what you suggest, however, my situation is, the falling path is {from emif|ddr_inst|hmc.amm.data to emif|ddr_inst|phy_register}

this path is generated during compile, so I can't see it in qsys, all I can see is just a bus to EMIF IP.

It's from ddr_inst to IO pad phy_register.

I have try over constraint

if {$::quartus(nameofexecutable) != "quartus_sta"} {set_max_delay -to {board_inst|acl_ddr4?_s10|acl_ddr4?_s10_emif_s10_0|acl_ddr4?_s10_emif_s10_0|arch|arch_inst|io_tiles_wrap_inst|io_tiles_inst|tile_gen[?].lane_gen[?].lane_inst|lane_inst~phy_reg1} 3.000ns }

but still won't help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi HHo2,

Can you check below EMIF spec estimator link to ensure your DDR4 IP configuration is within the spec ?

Once you confirmed you are using valid DDR4 IP setting then you can easily generate DDR4 example design from DDR4 IP using same exact setting. After that, you refer to the example design to get better clue on how to close timing.

Thanks.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page