- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As the FPGA I/O resource is limited, I translate LVDS signals to single ended type (LVCMOS) by external translator (TI SN65EPT23), and now I want to process the single ended signal with ALTLVDS_RX. Unfortunately, it seems that it can only receive differential signals from the I/O pins and can't receive signals after I/O buffer. The single ended signal speed is about 400Mbps (200MHz) and signal integration quality is good enough. So, what should I do?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Although I suspect it is a very bad idea, you could try the ALTDDIO_IN core. There is no reason to expect ALTLVDS_RX core to work with anything other than LVDS. I've used the ALTDDIO_OUT for DAC's that use single ended DDR signals and it works well.

You don't say what FPGA or how many SN65EPT23 chips you need, but your going to use a huge amount of extra board space and add alot of complexity to save a couple of FPGA pins. Does the SN65EPT23 have internal termination?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Corestar, Appreciated for your help. And here are some extra information:

#1. The FPGA I used is 5CGXFC7D6F27C7N;

#2. I used eight SN65EPT23, one can translate two LVDS signals to LVCMOS. I use eight LVDS data and eight LVDS synchronous clock. So, each SN65EPT23 translate one pair of LVDS data and LVDS clock to LVCMOS data and clock. Clock frequency is 1/10 data frequency; We want to use the synchronous clock to deserialize the data.

#3. There is no internal termination resistor in SN65EPT23, and I use external resistor for them.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@sYimi , I see what you are saying. That is alot of independent clocks (I'm assuming all the clocks are asynchronous). We use the Cyclone V GX as well, and the ALTLVDS_RX core will require you to have the LVDS clock on a clock input on a compatible bank to the data and will by default use a PLL. So even if it accepted single-ended inputs, you would run out of PLL's. So you will probably have to do clock domain crossing as well.

The next larger CV has 8 PLL's, but that does not leave anything for the rest of the design. However, the ALTLVDS_RX core has an option to use an external PLL. So you could use that on one or more of them and still generate other clocks if needed. It would cost a few dollars more, but save a vast amount of board space and complexity.

It's a shame, in addition to on chip termination, we user the hard IP LVDS to do deserialization. I don't know if it's possible to use those in your case. I'm afraid you need someone more knowledgeable than me to help at this point.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@corestar. Thanks for your great help, we are trying the ALTDDIO IP core now and hope it works. But I am still wondering is it possible to use ALTLVDS_RX to deal with this case. I know, the LVDS signals will be transferred to single ended type inside FPGA and then do deserialization because FPGA logic cell can only process single ended type signals. The only difference is that I use LVDS translator IC translate the signals and then input to FPGA. In fact, we can use one or two synchronous clock to collect all of the eight channel data.

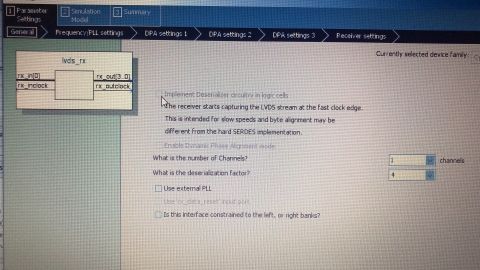

It is described that there is option "Implement Deserializer circuit in logic cell" in page ten of "LVDS Serdes Transmitter/Receiver IP cores User Guide", I guess if we can select this option we probably use single ended IO buffer output to feed in the ALTLVDS_RX IP core. Unfortunately, our firmware engineer told me it is unselectable for Cyclone V GX chip. You can check the attached picture and please help to check why?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In fact, we can use one or two synchronous clock to collect all of the eight channel data.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@sYimi , I'm a bit confused at this point. Could you clarify what is generating your LVDS data and clocks? It sounds like you have 8 data channels and 1 or 2 clocks.

The simplest solution by far is to simply feed those in as LVDS pairs and use the ALTLVDS_RX core(s) in the normal way. What is preventing you from just doing that? It would only be 10 extra pins and you are using a large package. But if that is the issue, in my opinion, you'd be far better of picking a larger package than adding all these extra chips to the board. I'm afraid I'm having trouble understanding the reason for using level shifting.

And if there are only 1 or 2 clocks, why are you using 8 SN65EPT23 and feeding a data/clock pair into each? Is there a version of the SN65EPT23 that will take 10 inputs?

If you really need to use your current method, the part-to-part skew of the SN65EPT23 is small enough that you may be able to get things working at 200 MHz, but are you sure your clocks are properly aligned? One thing the PLL in the LVDS core allows is to offset the clock so that it is properly centered on the data.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Corestar:

#1. The LVDS data and clocks are generated by other eight FPGA in other different PCB, and they are sent to the Cyclone V GX FPGA board by cable;

#2. I know I probably can solve this problem by upgrade the hardware design and use a FPGA has more I/Os. But I need to upgrade the hardware design which is time cost and also need to be verified. This type of FPGA are mass used in our products and I don't want to introduce new type of FPGA.

#3. There are eight individual synchronous clocks signals, but I think probably we can use only some of them to collect all of the eight channel data signals.

#4. There are only two LVDS input in one SN65EPT23, the maximum channel to channel skew is 110ps and part to part skew is 400ps.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@sYimi , I see, so you really are resource limited (as you clearly stated at the outset :-) ). There are not enough PLL's to do it the straightforward way.

Hopefully ALTDDIO_IN will work for you. So long as the clock/data pair from each FPGA is properly aligned, you should be able to make it work.

If you control both sides, any chance you could do it with transceivers instead of LVDS (I think you have 9) Would actually use fewer pins, but you'll have PLL issues ...

Maybe someone else will have a better idea.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page