- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

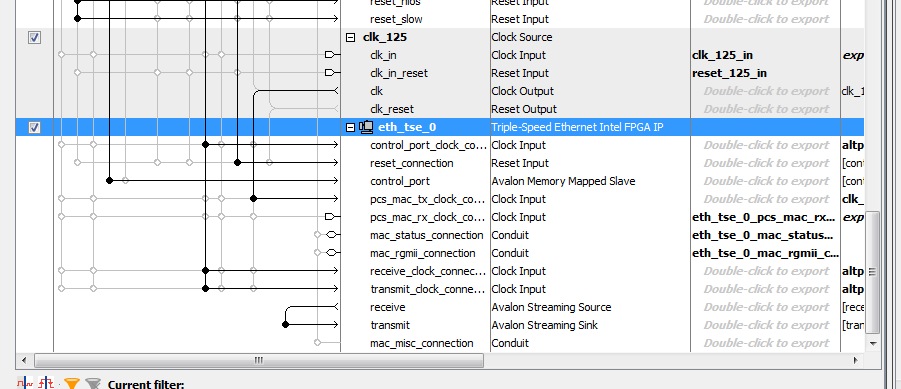

I am integrating the triple speed ethernet Intel Core into my design and I am having some timing problems.

My system is:

External Clk125 -> clk125 FPGA pin -> Clock Control -> Triple-Speed Ethernet Intel FPGA IP

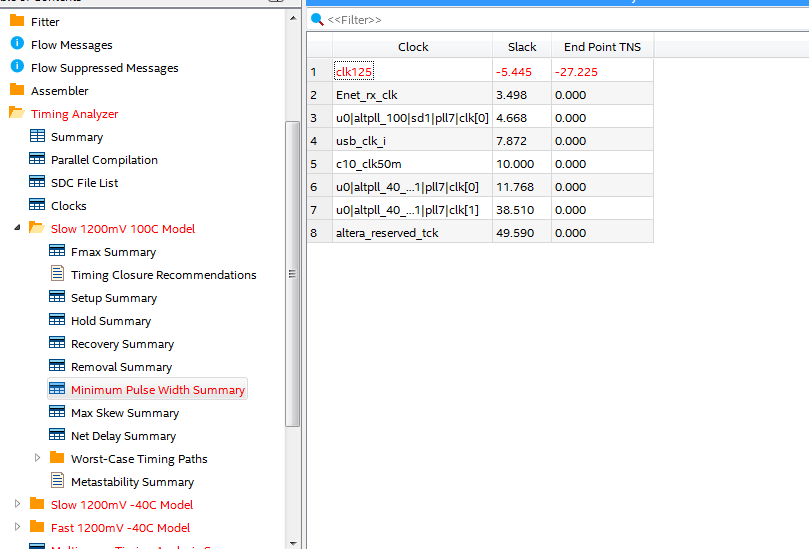

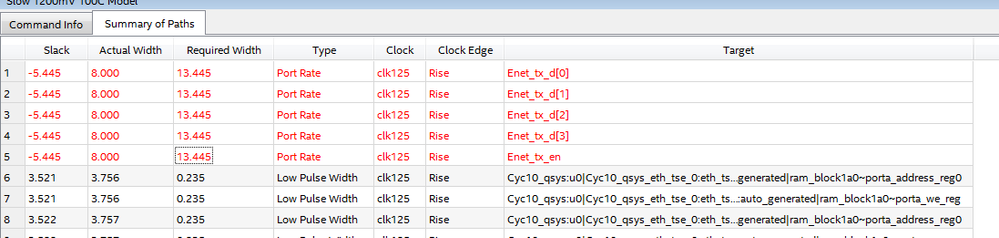

Then after fitting the design the compiler says that it has a Minimum pulse width Violation:

I run an analysis and it says:

So the problem is in the output data and enable signal of the Intel Ethernet CORE.

-Other interesting stuff that I found:

+--------------------------------------------------------------------------------------------------------------------+

; Slow 1200mV 100C Model Fmax Summary ;

+------------+-----------------+---------------------------------+---------------------------------------------------+

; Fmax ; Restricted Fmax ; Clock Name ; Note ;

+------------+-----------------+---------------------------------+---------------------------------------------------+

; 22.75 MHz ; 22.75 MHz ; u0|altpll_40_10|sd1|pll7|clk[1] ; ;

; 66.09 MHz ; 66.09 MHz ; u0|altpll_40_10|sd1|pll7|clk[0] ; ;

; 120.29 MHz ; 120.29 MHz ; u0|altpll_100|sd1|pll7|clk[0] ; ;

; 122.87 MHz ; 122.87 MHz ; usb_clk_i ; ;

; 126.2 MHz ; 126.2 MHz ; altera_reserved_tck ; ;

; 138.18 MHz ; 74.38 MHz ; clk125 ; limit due to minimum port rate restriction (tmin) ;

; 180.28 MHz ; 180.28 MHz ; Enet_rx_clk ; ;

+------------+-----------------+---------------------------------+---------------------------------------------------+

-How I can delete this restriction? I think that this is the problem.

-If you press in failing parts there is no failing paths, the problem is that the port has a timing restriction, so it doesn’t matter the path, just the output frequency.

I have a look on internet and I found this fix:

https://forums.intel.com/s/question/0D50P00003yyTDDSA2/minimum-pulse-width-error?language=en_US

It says to things:

- Use the command set_min_pulse_width -high 4.0 [all_clocks] set_min_pulse_width -low 4.0 [all_clocks] that is not recognized by Quartus/

- Change the current of the ports, I tried it and I set to the maximum and it helps during 2 compilations (the slack was reduced by 2) but it didn’t totally fix the problem and after two compilations it returned to the initial slack.

Thanks.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

From the example design that download from the Intel FPGA design store, the timing is clean. You may refer to the following link, and check where is the trigger point for this timing problem.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

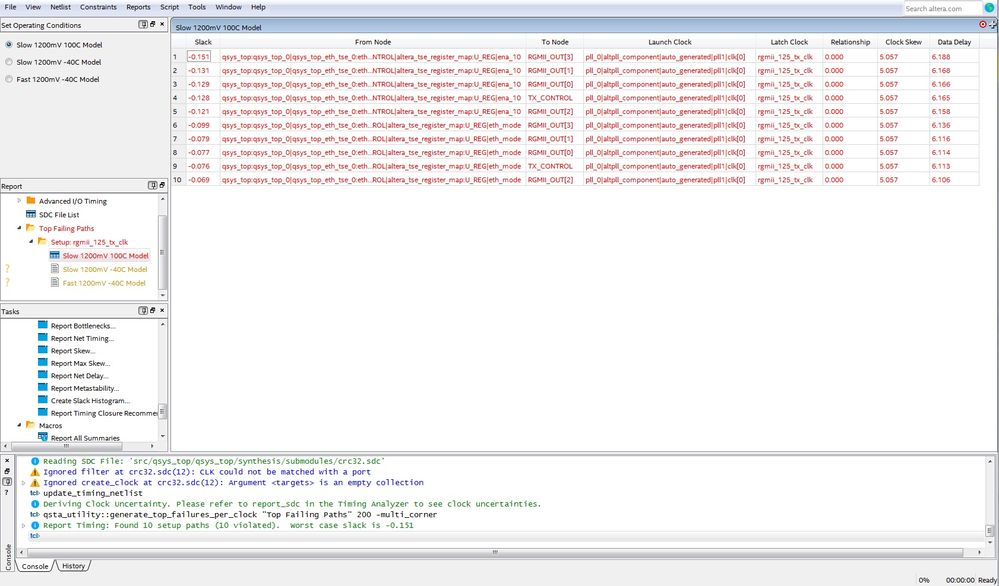

I compiled the "clean build" and it also has timing problems:

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page