- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, I just started on VHDL about a month ago and I'm making a base 12 to base 6 converter as a part of my school project, this is what I currently have:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity R12_3digToR6_4digConv is

port(

d : in STD_LOGIC_VECTOR (11 downto 0);

n : out STD_LOGIC_VECTOR (15 downto 0)

);

end R12_3digToR6_4digConv;

architecture arch_R12M7A9_3digToR6_4digConv of R12_3digToR6_4digConv is

signal d_sum10,d_temp,d_sum6 : integer := 0;

begin

process(d)

begin

--Getting digits and converting to base 10

d_sum10 <= to_integer(unsigned(d(11 downto 8))*"10010000" + unsigned(d(7 downto 4))*"1010" + unsigned(d(3 downto 0)));

--Convert base 10 to base 6

for i in 0 to 3 loop

d_temp <= d_sum10 mod 6;

d_sum10 <= d_sum10 / 6;

n((15 - 4*i) downto (12 - 4*i)) <= std_logic_vector(to_unsigned(d_temp,4));

end loop;

end process;

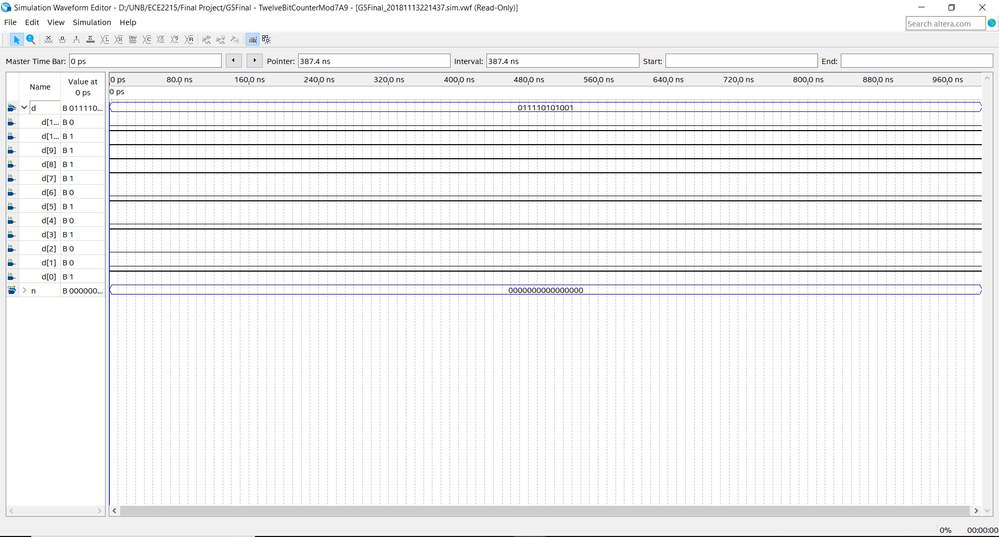

end arch_R12M7A9_3digToR6_4digConv;It compiled fine but it doesn't give me the expected result, in the image I have bin set to "011110101001" (7A9) in base 12 and I expected it to return "0101000100110011" (5133) in base 6 as the output, but it gave me 0s. Any suggestion would be great, thank you :).

Link Copied

1 Reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you debug the signal 'd_sum10' ?

Check whether Conversion of base 12 to base 10 happening correctly...

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Best Regards

Vikas Jathar

(This message was posted on behalf of Intel Corporation)

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page