- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

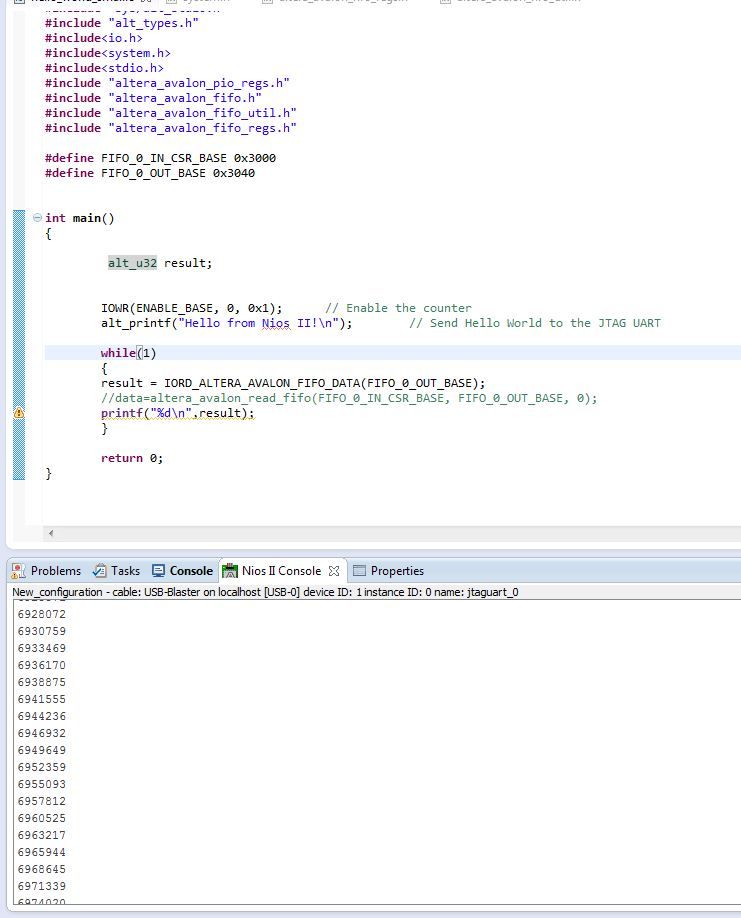

I want to write 32-bit data into FIFO and read the data from FIFO.

So, I have followed this FIFO configuration :Aalon-MM write slave to Avalon-MM read slave.

Questions to be clarified:

- I have enabled "backpressure" how to set in wait request signal in NIOS (0`s (deserted) or 1`s (asserted)).

2. i want example code to read the data from FIFO. I have tried but its throwing error. "FIFO_0_IN_BASE" is undeclared.

in which file i can find Base address and control address for read operation.

Please anyone guide me.

#include "sys/alt_stdio.h"

#include "alt_types.h"

#include<io.h>

#include<system.h>

#include<stdio.h>

#include "altera_avalon_pio_regs.h"

#include "altera_avalon_fifo.h"

#include "altera_avalon_fifo_util.h"

#include "altera_avalon_fifo_regs.h"

#define FIFO_0_IN_BASE 0x3000

#define ctrl_address 0x3040

int main()

{

int result,i=0;

int *data=0;

IOWR(ENABLE_BASE, 0, 0x1); // Enable the counter

alt_printf("Hello from Nios II!\n"); // Send Hello World to the JTAG UART

while(1)

{

*data = IORD_ALTERA_AVALON_FIFO_DATA(FIFO_0_IN_BASE);

printf("%d\n",*data);

}

return 0;

}

Link Copied

2 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The base addresses are defined in the 'system.h' file (that you already have in your #include list).

Cheers,

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page