- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

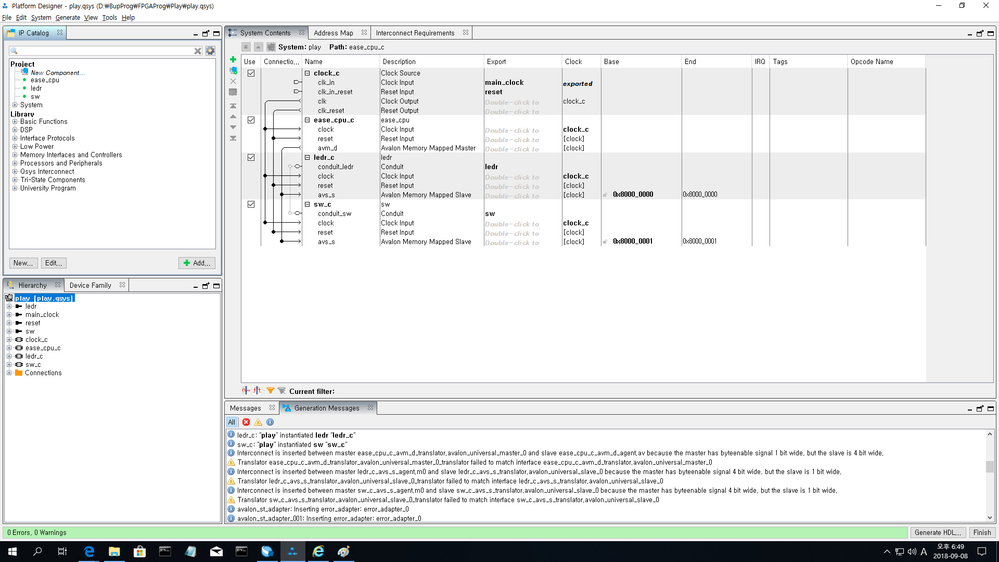

I'm creating my custom "CPU" and peripherals with Platform Designer, and connecting them using Avalon Memory-mapped bus.

For simplicity, my CPU always uses and transfers 32-bit data, and there are no "byte-enable" signals. Therefore, I thought "32 bits per symbol" is reasonable choice.

I created custom peripherals for LEDs and slide switches included in DE10-Lite evaluation board (which uses MAX-10 FPGA), and they also uses 32 bits per symbol.

However, when I generate HDL files, I got following warnings:

[Info] Interconnect is inserted between master ease_cpu_c_avm_d_translator.avalon_universal_master_0 and slave ease_cpu_c_avm_d_agent.av because the master has byteenable signal 1 bit wide, but the slave is 4 bit wide.

[Warning] Translator ease_cpu_c_avm_d_translator_avalon_universal_master_0_translator failed to match interface ease_cpu_c_avm_d_translator.avalon_universal_master_0

[Info] Interconnect is inserted between master ledr_c_avs_s_agent.m0 and slave ledr_c_avs_s_translator.avalon_universal_slave_0 because the master has byteenable signal 4 bit wide, but the slave is 1 bit wide.

[Warning] Translator ledr_c_avs_s_translator_avalon_universal_slave_0_translator failed to match interface ledr_c_avs_s_translator.avalon_universal_slave_0

[Info] Interconnect is inserted between master sw_c_avs_s_agent.m0 and slave sw_c_avs_s_translator.avalon_universal_slave_0 because the master has byteenable signal 4 bit wide, but the slave is 1 bit wide.

[Warning] Translator sw_c_avs_s_translator_avalon_universal_slave_0_translator failed to match interface sw_c_avs_s_translator.avalon_universal_slave_0

It seems that something is trying to connect 1-width byteenable to 4-width byteenable, and then 4-width byteenable to 1-width byteenable.

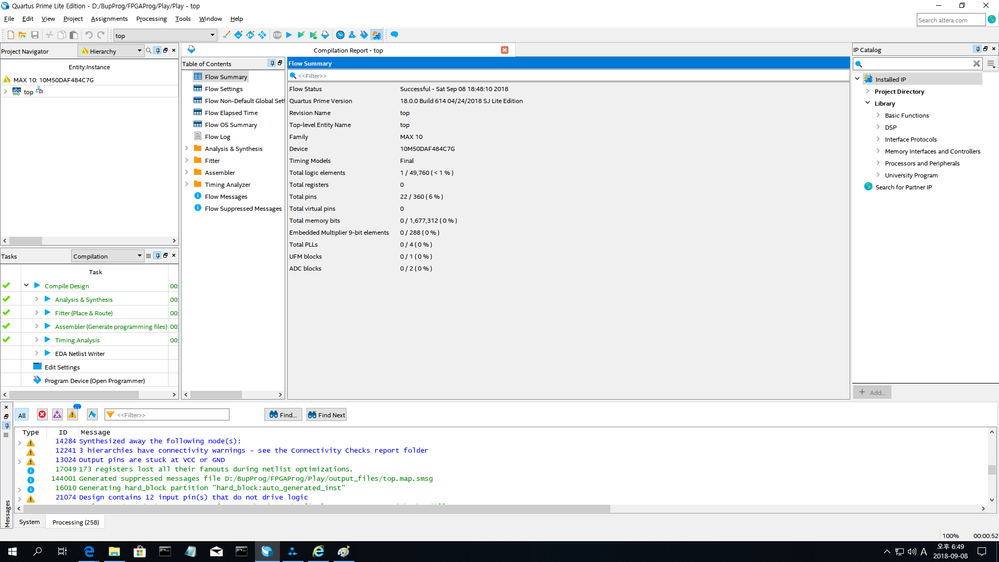

Moreover, the whole synthesis step produces nothing; even clock and reset signal didn't used.

I suspect that there are some issues regarding "custom" bits per symbol other than 8, but I'm not sure whether I made some serious mistake.

From now, I'm trying to change my design to use "8 bits per symbol" settings and see what happends. While it might took soem times, until then, could you guide me what am I doing wrong?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It seems that (almost?) all existing components in stock library requires 8 bits per symbol; it doesn't allow to connect components that have different bits per symbol width.

So, I withdraw this question, and will change bits per symbol value to 8.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It seems that (almost?) all existing components in stock library requires 8 bits per symbol; it doesn't allow to connect components that have different bits per symbol width.

So, I withdraw this question, and will change bits per symbol value to 8.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page