- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have a design which compile and fit properly in Quartus_19.1.0.670 version.

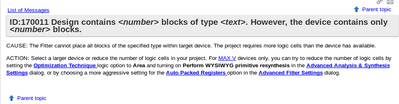

But exactly same design does not fit when I use Quartus-21.1.0.842. It gave me following error.

I tried many settings in synthesis and fitter, but none worked for me. Any suggestions?

Regards,

Vikram

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How full was the device in 19.1? I'm guessing very full. It's possible some optimization did not occur when you moved to the new version or the function of a particular optimization changed.

Or are you using design partitioning/block-based design or Logic Lock regions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also, you're showing the generic message, not the actual error message. What resource is Quartus saying you are overusing?

You should also try, at least temporarily, disabling design partitioning to see if that is part of the issue (which I'm guessing it is).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the reply.

In 19.1 its about ~55% full. Its certainly not the design going beyond the capacity. With ease we can fit it in 19.1 and its prior version 15.1 which I have installed.

Its partitioned well, block based. I am not using Logic lock functionality, each time I do Quartus synthesis and fitting. Constraints file looks just fine.

Very much puzzled with latest version. Started thinking now, might be a Quartus bug itself?

Regards,

Vikram

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Vikram,

May I know what version you are using?

Is it possible to provide qar design file/ small design to replicate at my end?

From my pov, this seem optimization issue in current Quartus which probably not fully optimized the logic.

Does the same thing happen if you are redesign directly (not migrate) from latest build used?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Vikram,

It would be a good if there is a fitter report so that you can see what resources used more.

As suggested, have you able to disable the design partitioned and see if thats the root cause?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The exact error message I get is this

Regards,

Vikram

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Vikram,

May I know if it is possible to have the qar design for me to replicate?

This could be a good test case for Quartus enhancement.

You may attach it here in zip or reply to my email and attach there.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The qar file just showing only this.

emif_restrict_hps_refclk_to_ac_tile = off

Should I use some settings to get more info in qar file?

Regards,

Vikram

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Vikram,

Let me know if there is any update from my previous reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We do not receive any response from you to the previous reply that I have provided, thus I will put this case to close pending. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page