- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I try to use Quartus 22.1 on Linux for the target 5CSEBA6U23I7.

Simulations work when I use Tool > Run Simulation Tool > RTL Simulation.

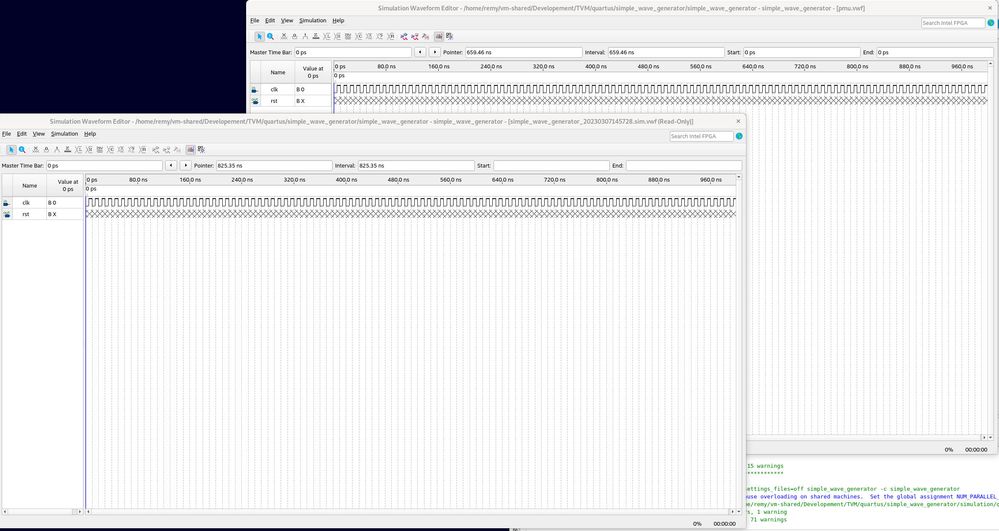

But when I want to simulate a University Program VWF, outputs stays to undefined on the window which popups at the end of the simulation.

Is it a common issue ?

Best regards

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you established any output in the waveform window?

You may need to add node for output using node finder by right click --> insert node or bus --> choose your input/output

Any snapshot on the issue maybe if possible?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes I had added each input/output before to launch the simulation. The output stays just to undefined.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Without seeing the design, there's no way to know what's going on here. Can you provide the code?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here the used code.

library ieee;

use ieee.std_logic_1164.all;

entity pmu is

port(

clk : in std_logic;

rst : out std_logic

);

end pmu;

architecture rtl of pmu is

begin

rst <= not clk;

end rtl;Thank you for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Remy,

From the snippet code given, the output of the rst signal will stay at an undefined state during because it is being driven by a combinational logic circuit that depends on the clk input signal.

To fix this issue, you can use an initial value for the rst signal in the architecture. For example, you can add a default initial value of '0' to the rst signal declaration, like this:

entity pmu is

port(

clk : in std_logic;

rst : out std_logic := '0' -- add default initial value

);

end pmu;

architecture rtl of pmu is

begin

rst <= not clk;

end rtl;

This will ensure that the rst signal is initialized to a known value at the beginning of the simulation, preventing it from being in an undefined state.

p/s: If any answer from the community or Intel Support are helpful, please feel free mark and solution, give kudos and rate 5/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As I said in my first message:

"Simulations work when I use Tool > Run Simulation Tool > RTL Simulation. The issue appears only when I use University Program VWF, outputs stays to undefined on the window which popups at the end of the simulation."

So I have already verified if it is a VHDL issue and it is not. For example, even if I put:

architecture rtl of pmu is

begin

rst <= '1';

end rtl;this changes nothing...

For me, it is a tool issue. It seems there is a communication issue between the simulator and the viewer.

I just want to know if it is a known issue and if there is a solution.

Thank you for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello. I have the exactly same problem with vwf simulation in quartus 22.1 on linux.

The output stay X after I "Run a functional simulation".

Note that i remove the -novopt option in order to make it run without error. i don't know whether this matter or not to the stay X problem.

note that in 2nd image i send. That the right window's "Run Functional Simulation" gray out. Indicate that is simulation result.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Remy,

Seem there is issue with VWF tool, I will report this to developer for fix.

Is using Modelsim simulation work for you?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, I think it works fine.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Glad that is working fine. Let me know if there is any other concern

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page