- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

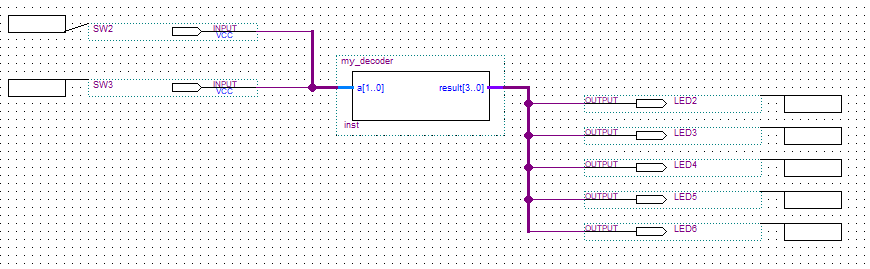

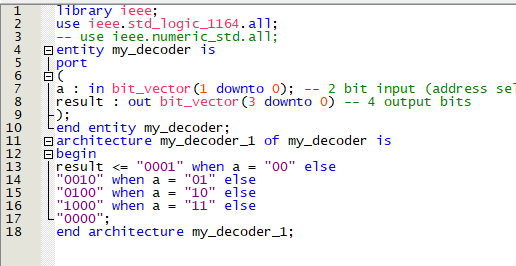

I am a first year electronics university student who is completely new to Quartus and VHDL. We have a list of tutorial sheets to follow and even though I have followed the step by step instructions am still generating the two error messages. I have absolutely no idea where to start so any advice would be extremely helpful. The attached images are of my VHDL code and top-sheet on Quartus. The fuller error messages are:

Error (275044): Port "a[1..0]" of type my_decoder of instance "inst" is missing source signal

Error (12153): Can't elaborate top-level user hierarchy

- Tags:

- Vhdl

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, your issue are on your design not on tool.

These error are related to your instance assigning pin to VCC, output vector 3 downto 0 is 4 element on output where 5 element..

VHDL has nothing wrong, so it can work, assign pin by pin planner or if you prefer bdf, remove VCC from a and connect where this has to be.

Not Quartus related. Please don't flood topic have nothing to do here, is better on vhdl forum.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The problem is in your top level schematic. You're doing bit slicing for the wires (inputs and outputs), but you haven't named the wires, so the tool has no idea how to connect the inputs to "a" and the result outputs to the LEDs. To fix this, right-click the wires connected to the switch inputs and LED outputs, and open the wire properties. Give each one a name that matches the appropriate bits, like a[0], a[1], result[3], etc. You could also instead change the names of the inputs and outputs themselves to these names. Also, you have 5 LED outputs connected to a 4-bit bus, so I'm not sure what's going on there.

Once the names match, the tool will know which bits to connect to which I/O. That's the problem with the design as it stands right now.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

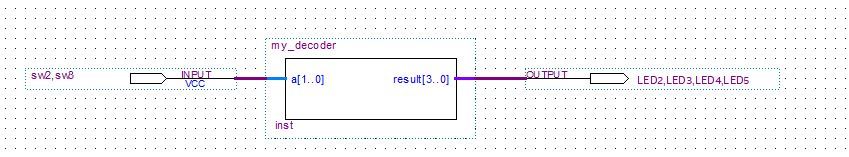

Just insert symbol "my_decoder" & rename inputs & outputs as shown below,

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you resolved the issue?

Should I consider that case to be closed?

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vichy, from this post I realized no Quartus usage nor beginner forum spacialized space. ( I think forever useful to learn about something new also to experienced.)

(Quite Off Topic, no space found as it where on Altera)

FPGA is this way spreading over colleges, so University program I think is no more enough to split forum traffic on basic question.

Ask about on your side if this appear a good way to help who is starting learn tool.

Non tool related deterministic design error are simple to solve. Tool related when are not simple to catch turn out to a nightmare.

IMHO porting Altera knowledge base to intel site lost a lot of what was on a small community. So large site spreaded information over interspersed into different scene, everyone post was adsorbed as (intel), so I am not working @ Intel but my old post where classified as Intel.

FPGA need a separate site dedicated to it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Roberto,

I appreciate your suggestion, feedback/suggestions are always welcome.

In fact, suggestion/feedback facility has been given to members of Intel community please navigate as,

Community -> Help and FAQs -> Website feedback or report a problem

Regards,

Vicky

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page