- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i have a simple sv code, which has assertions

module top(input [2:0] in1, input [2:0] in2, output [3:0] out1, input clk);

parameter p1 = 4;

parameter p2 = 5;

reg [3:0] out1_reg;

always @(posedge clk) begin

assert(p1 == p2)

else

$error("fail");

end

assign out1 = out1_reg;

//assign out1 = in1+ in2;

endmodule

I have enable the asseriotion, under assignements->settings->compiler settings-> advanced options.

when i run the above code i dont see any error message.

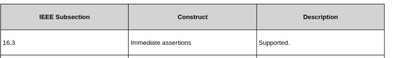

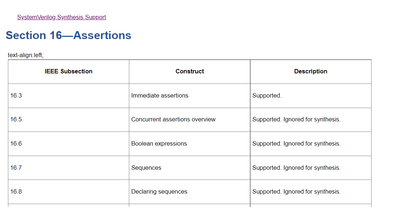

and i see assertion is supported

am I missing something, while using assertion?

- Tags:

- SV assertions

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What are you expecting? assert is used for simulation, not synthesis.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the snippet it is mentioned as supported and it does not say ignored by synthesis, was expecting it prints out the message in log.

Immediate assertion is similar to if statements, so was expecting some logic is generated

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If I'm not mistaken $error is from SystemVerilog-2005. This is only supported on Quartus Prime Pro.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We did not receive any response to the previous question/reply/answer that I have provided, thus I will put this case to close pending. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

Regards,

Nurina

P/S: If you like my comment, feel free to give Kudos. If my comment solved your problem, feel free to accept my comment as solution!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page