- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, we’re facing the following problem.

We’re developing the project with SDI 12G output signal on base Cyclone 10 GX FPGA.

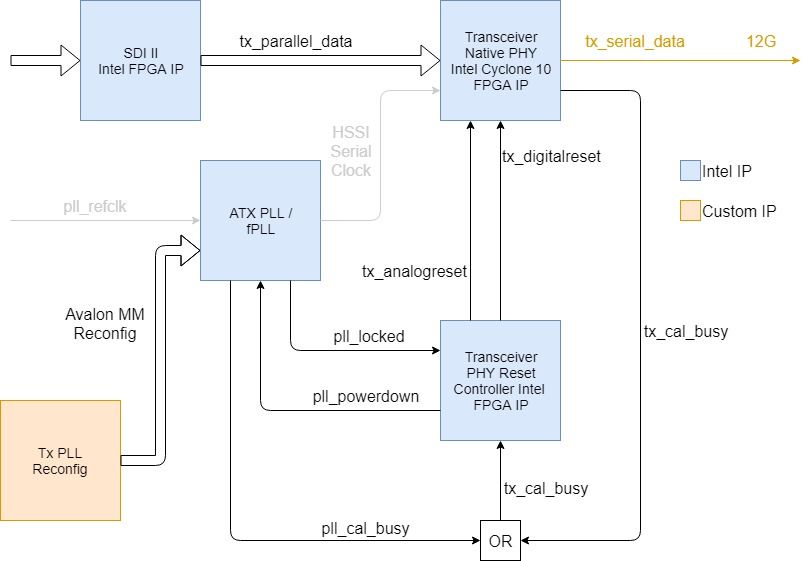

We use the Intel IP for SDI protocol, Transceiver PHY and Tx PLL. Here you can see the common architecture of the project:

It works well, but sometimes we get bad jitter performance on the 12G output. It happens when we do the Tx PLL recalibration process.

After recalibration finished we can get either good jitter (less than 0.21 UI) or bad one (more than 0.3 UI).

We don’t know what it depends on. The recalibration process is the same and there aren’t any differences between cases.

Accordingly to the Intel Cyclone GX 10 Transceiver PHY User Guide (UG20070) we tried to improve jitter following next steps:

- Use ATX PLL instead of fPLL because ATX PLL has better jitter performance;

- Set Transmitter High-Speed Compensation option to Enable for corresponding Tx serial data out pin.

But no one of these steps helped us.

Could you give us any advice what else we can do to influence jitter performance, please?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you have some inquiries related to the jitter performance with the 12G SDI TX output in C10GX device. For your information, the following are the possibilities that I could think of for your reference:

1. Input refclk - Potential SI or jitter problem at the input refclk would propagate into the TX PLL and then impact the TX output jitter. It is recommended for you to measure the eye diagram using oscilloscope at the FPGA input refclk to check if there is any anomaly.

2. Dedicated input refclk - The dedicated input refclk pin for the transcevier will have the best performance as compare to other type of refclk input ie RX pin, refclk network. You can try to switch to dedicated input refclk pins if you are not using them currently.

3. Just to check if you are running a single channel SDI TX or if you have multiple channels? If there are multiple channels, it is recommended to try with single channel only to see if things improve to narrow down any potential crosstalk problem.

4. Just to check if the TX PLL refclk and the CLKUSR are directly sourced from on-board free running and stable oscillators? This is the ensure successful power up calibration for TX PLL and transceiver channel.

5. If you are using ATX PLL, you can try with different Bandwidth setting to see if there is any difference.

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, it has been some time since I last heard from you. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page