- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The issue is that the MPU IP was updated at some point, however, the documentation, the example code and most importantly, the Nios 2 register definitions (contained in nios2.h) have not been updated. The first two probably wouldn't have mattered so much, because a user might not have noticed if the register definitions were correct. I've only checked version Quartus 20.1

Furthermore, the MPU documentation appears to be split across 4 or 5 different documents and application notes, each with varying degrees of accuracy. To save you the search, the most accurate description of the MPU is in the embedded design handbook.

This document describes a different layout to the mpubase and mpuacc registers compared to every other document. For example:

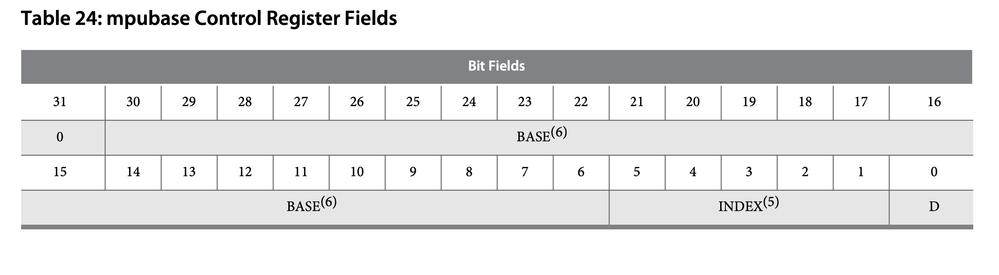

Example of old mpubase register

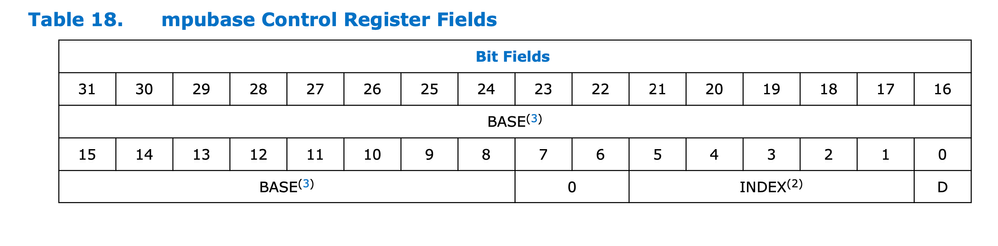

Example of new mpubase register

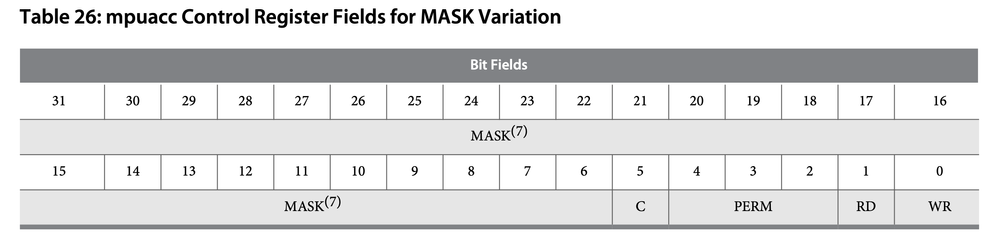

Example of old mpuacc register

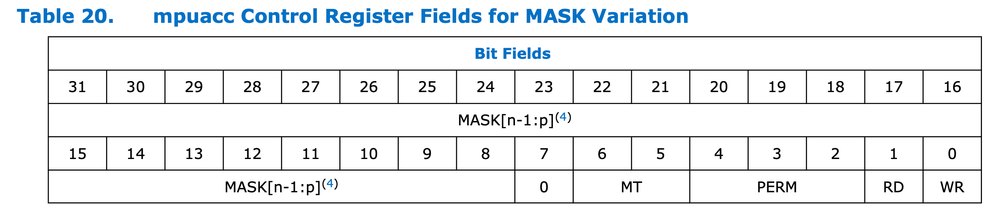

Example of new mpuacc register

So it appears that these registers were updated in the IP, but not in the BSP and so if you try to use the examples in AN540 (which the embedded design handbook still refers to), they won't work. You'll need to either update the register definitions in nios2.h or instead, edit mpu_utils.c and mpu_utils.h in order to get it to work. I chose to edit the mpu_utils files as these are not part of the BSP and thus won't revert back after regenerating the BSP.

I've attached the edit files here.

One other thing I noticed about the base calculation. The document states:

BASE = <base address>/<min_region>

For example, if the region starts at 0x1000 and the minimum region size is 256 bytes,

set the BASE field to 0x10, which is 0x1000/256.

I have found that in order to calculate the correct base value, the base address is always divided by 256 bytes, regardless of if you have set the minimum region size to something larger.

Hopefully this post will save people time trying to figure out why the MPU doesn't work for them and hopefully Intel can update their documentation, BSP and examples soon.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Broddo,

Thank you for posting in Intel community forum, hope this message find you well.

Much appreciate on the effort to share the finding for mention behavior in MPU IP.

We have take noted on this and will improve it in the future version as well as updates the document as relevant.

As there is no further issues on this this thread will be moved to community support for further queries, and new queries please do open a new thread to get support from Intel experts.

Best Wishes

BB

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page