- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

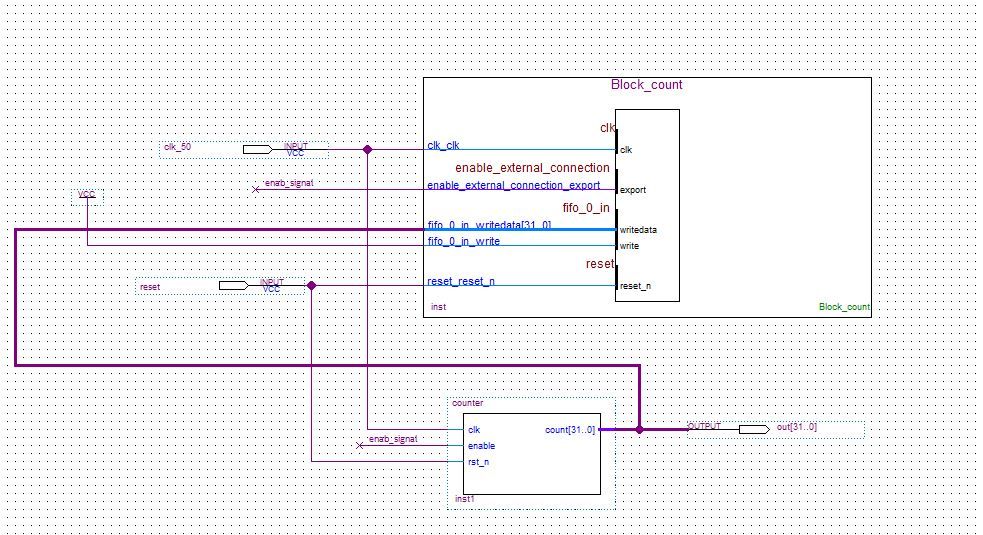

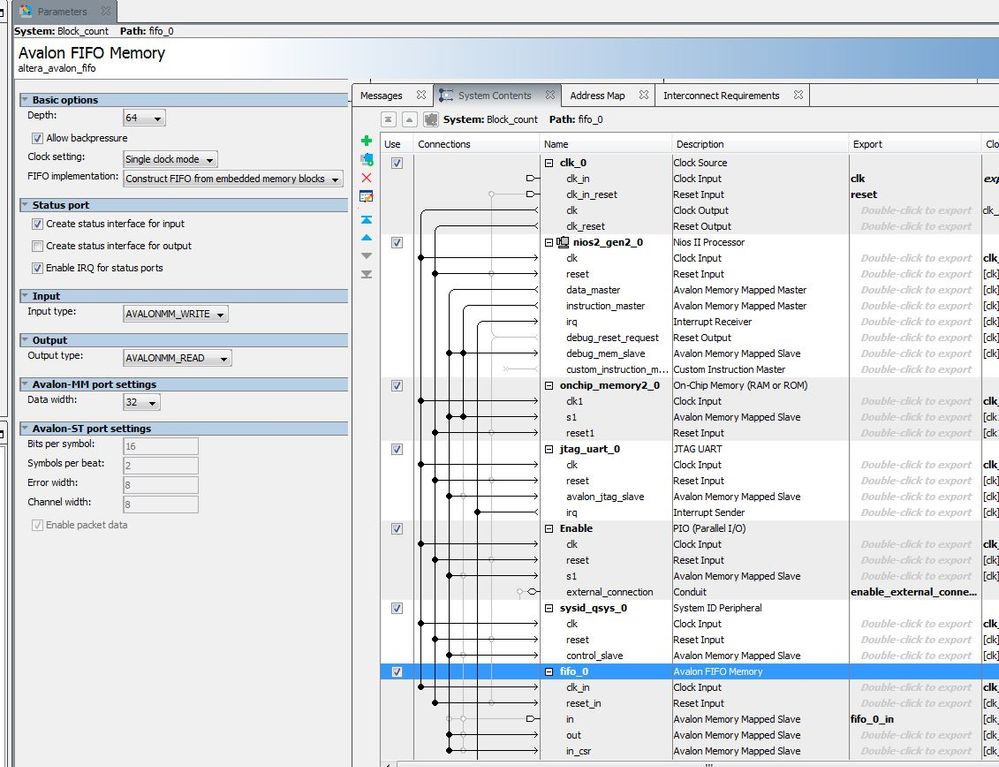

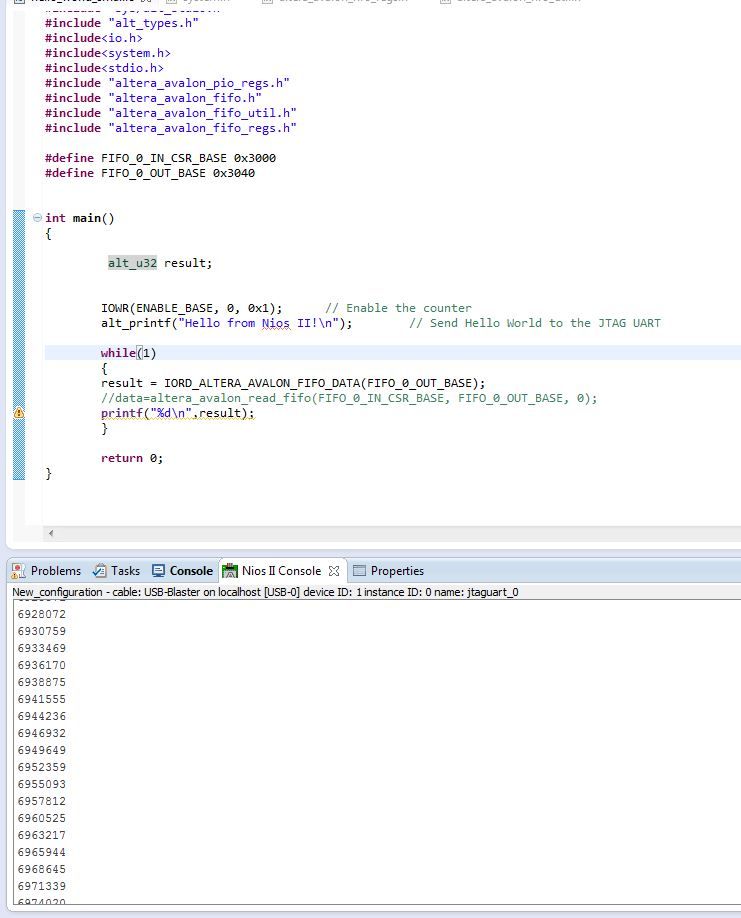

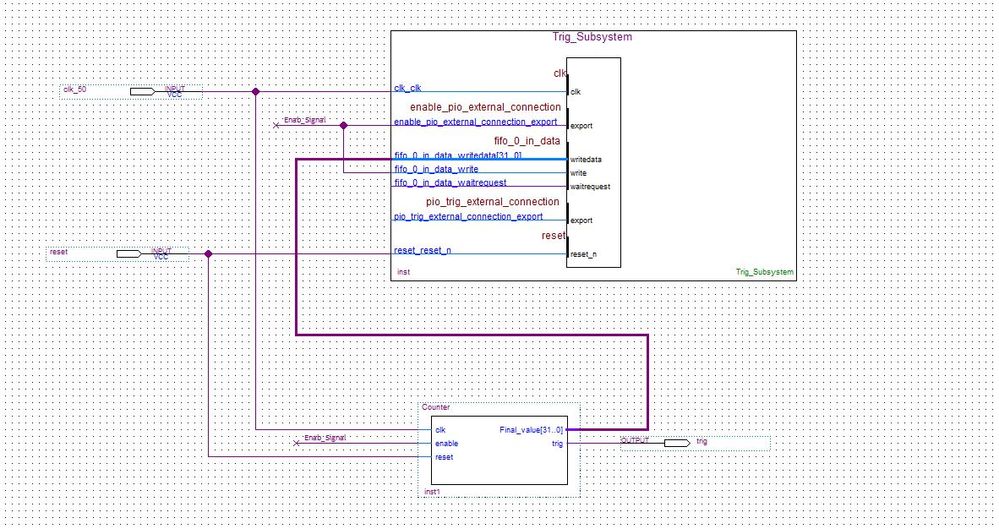

I want to write 32-bit data into FIFO and read that data from FIFO. [FIFO configuration :Aalon-MM write slave to Avalon-MM read slave.]

I have tried the below design but data is not in proper sequence.

Please anyone guide me.

Clock:50 Mhz

Design Flow as follows

Block design

Quartus

Qsys Design,

NIOS console

Data is not in Proper sequence. I dont know where its going wrong ?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You can try out the example here https://www.intel.co.jp/content/dam/altera-www/global/ja_JP/pdfs/literature/ug/ug_nios2_flash_programmer.pdf to see if you able read the correct memory.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You write to the fifo faster than you read back from it, so you will miss a lot of the counter values. In your design the write signal is always 1, meaning you write a value on each clock cycle. On the other side, as you are using a CPU to read back the data, there will be multiple clock cycles between two reads.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Daixiwen. Thanks for your response. If you could tell me the solution to sort my problem means, it will be helpful to me.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can't write on each clock cycle. You should change your design to check whether the fifo is full or not and only write the value (and increment the counter) when the fifo is not full.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

>>You should change your design to check whether the fifo is full or not.

I am new to the Altera. So can you tell me how can the design should be modified, or else any design examples. Please guide me step by step.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Daixiwen, I am able to print counter data in NIOS console.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

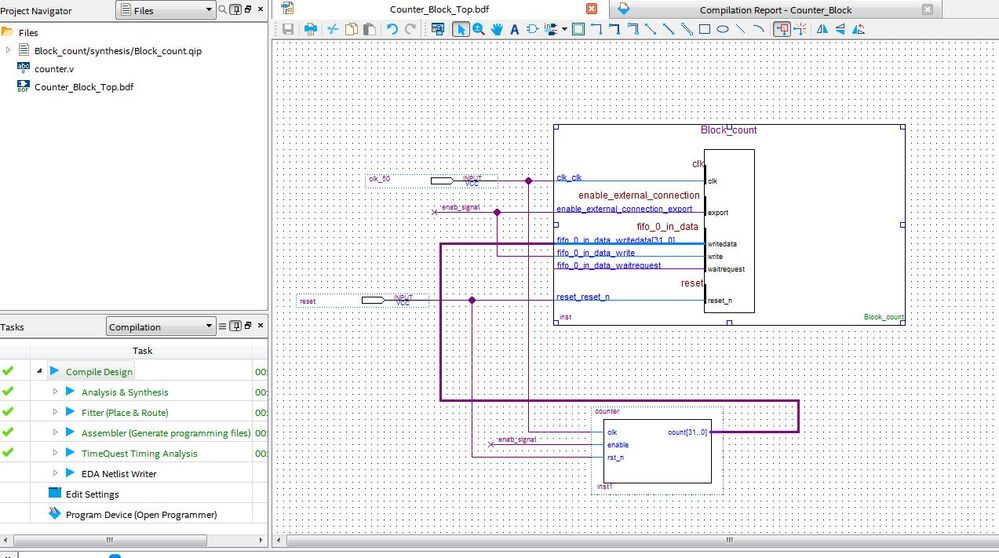

@Daixiwen. The above FIFO design is working. LIKEWISE, i have tried the same design.

Working Design BLOCK diagram

In following design, i am generating Trigger signal (500ns) and Counter data using Verilog code. Then need to read the data in NIOS console using FIFO.

Code

module Counter(

input clk,

input enable,

input reset,

output reg[31:0] Final_value,

output reg trig

);

reg[31:0] counter_out;

reg [7:0] temp;

reg [31:0] counter_result;

wire temp1;

wire temp2;

always@(posedge clk or negedge reset)

begin

if(~reset)

begin

trig<=0;

temp<=0;

counter_out<=0;

end

else if(enable==1'b1)

begin

counter_out<=counter_out+1;

temp<=temp+1;

if(temp==25)

begin

temp<=0;

trig<=~trig;

end

end

end

assign temp1=trig;

assign temp2=temp1&&clk;

always@(posedge temp2 or negedge reset)

if(~reset)

counter_result<=0;

else

begin

counter_result<=counter_result+1;

end

always@(posedge trig or negedge reset)

if(~reset)

Final_value<=0;

else

begin

Final_value<=counter_result;

end

endmoduleFIFO DESIGN [NOT working]

Can anyone point out me the error in my design. Please suggest me.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page