- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I want to know timing of specific path between registers to implement asynchronous circuit.

Following block is seen as register, so that it is exist in matches list in Name Finder in Timing Analyzer. So, I can know the timing information between this register and another register.

lut_input lut_in1 (a, wa);

lut_input lut_in2 (b, wb);

lut_input lut_in3 (y, wy);

lut_input lut_in4 (l, wl);

lut_output lut_o ((~wl & wy) | (wl & (wa | wb)), y);

However, following block is not seen as register. What should I do to see this block as register?

lut_input lut_in1 (l, wl);

lut_input lut_in2 (q, wq);

lut_input lut_in3 (s, ws);

lut_input lut_in4 (r, wr);

lut_input lut_in5 (mr, wmr);

lut_output lut_o ((~wl & wq) | (wl & ((~ws & wr & wmr) | (wq & ws) | (wq & ws & wr & wmr))), q);

I’m using Cyclone V GT.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I request the design.qar for investigation?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for replying.

I create simple sample project. Please refer to this design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have filed a case to the engineering team.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you please let me know the progress of this case?

Thank you very much in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Below is the feedback:

You either need to change the design not to have loops/latches, or else define a clock in the SDC. Right now, it sounds like Quartus is creating a dummy clock of some period to feed the latches.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for letting me know the feedback.

I have tried both ways: removing loop/latches (designA.qar) and defining a clock (designB.qar), but they did not work and I still can’t get the timing information between the specified latches (S1R2FFLN modules).

I wonder if I have done it in the right way.

I attached the .qar files of both trials to this post.

Could you please check my procedure and let me know if your find any problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

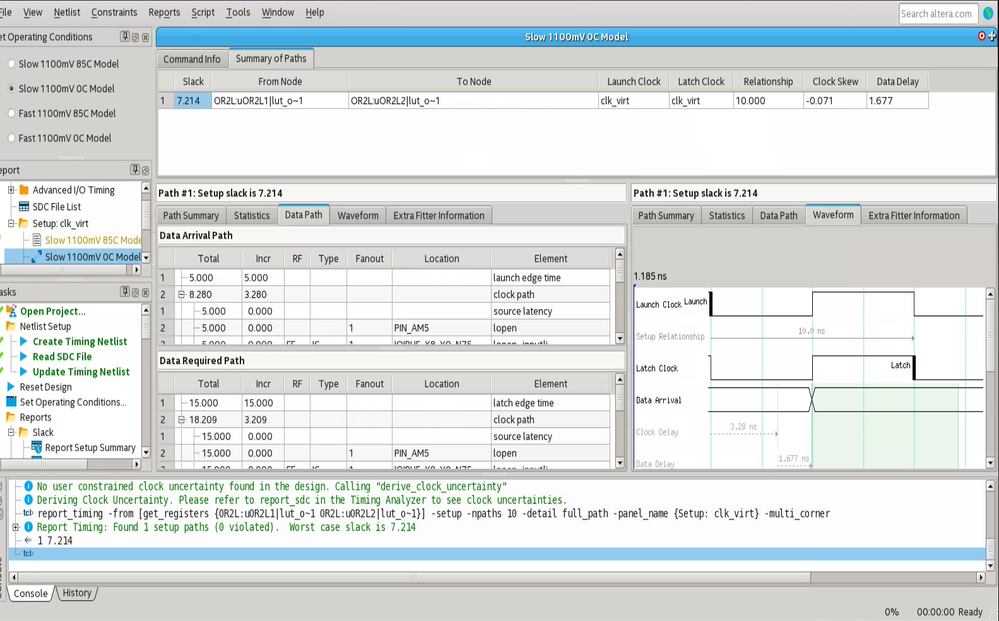

The Timing analyzer in the second design is analyzing the timing between S1R2FFLN modules.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page