- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

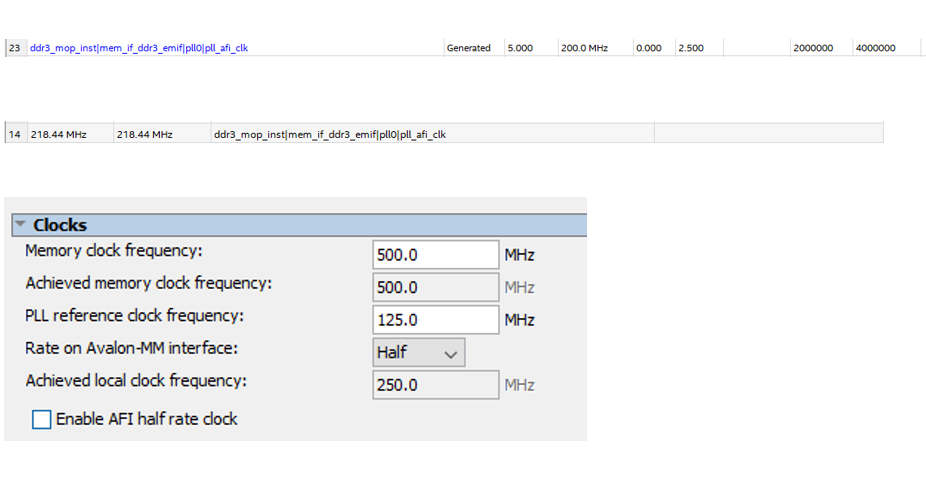

In Qsys I specify the "Memory clock frequency" as 500MHz. After compilation I run the timing analyzer, when I run "Report Clocks" it shows:

DDR3_CK: 400MHz

pll_afi_clk: 200MHz

When I run "Report Fmax Summary" it shows:

pll_afi_clk: 218MHz

It "passes" timing with Fmax of 218MHz. This is insufficient when mem_ck is really 500MHz and afi_clk is half that rate at 250MHz. I scoped mem_ck on our board and confirmed it being 500MHz which is what I specified in QSYS.

What is the cause for this discrepancy in the timequest analyzer?

Quartus Prime Standard 17.1 and 18.1

ArriaV GZ

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Vince,

Thank you for joining this Intel Community.

I can see you are using Half rate on Avalon-MM interface. For half rate, the maximum supported frequency for DDR3 is 400 MHz which means 500MHz is not supported for this type of interface. That's the reason you see below setting after compilation.

DDR3_CK: 400MHz

pll_afi_clk: 200MHz

For more details, you can refer to this EMIF spec: https://www.intel.com/content/www/us/en/programmable/support/support-resources/support-centers/external-memory-interfaces-support/emif.html

I am truly sorry for the inconvenience caused.

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your response, I have overlooked that the max rate is 400MHz. Unfortunately, when I enter 400MHz into Quartus the Timequest Analyzer still exhibits the same behavior of showing the clock summary at 80% of the 400MHz.

DDR3_CK: 320MHz

AFI_CLK: 160MHz

This would still cause issues as the .sdc is specifying the AFI_CLK at a lower frequency so the logic is not being optimized to run at the correct frequency. What is causing this discrepancy?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vince,

May I know what is the speed grade of the device used? It would be better if you can share with me the full part number of the device 😊

Also, is there other clock source used beside afi_clk? The reason I ask this because using another clock would cause Qsys to automatically instantiate clock-crossing logic, potentially degrading performance.

Regards,

NAli1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page