- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was using Quartus Prime Pro 18.1 edition and noticed the chip planner doesn't have the bird's eye view routing for analyzing the routing congestion.

The view routing feature is only available when with further zoom-in and can only see a portion of the routing in the zoom-in area. It is not a bird's eye view routing that can provide the overall routing congestion picture.

I saw there is a "Highlight Routing" feature mentioned in the Quartus Prime Pro Chip Planner youtube video and in the pg17 of Quartus II Handbook (QII52006-13.1.0):

https://www.youtube.com/watch?v=z82t12RCY_o

I would like to seek advice on the following three doubts here:

1. Does the "Highlight Routing" feature in a later version has the bird's eye view routing for analyzing the routing congestion?

2. If the "Highlight Routing" feature can't provide the bird's eye view routing, may I know does the "Report Routing Utilization" in the Chip Planner can be used to analyze the routing congestion? OR what are the tools in Quartus that can be used for analyzing routing congestion?

3. Which Quartus Prime Standard and Pro version started to has the "Highlight Routing" feature?

Thanks!

~Cheer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You have to find and highlight a path. You can search right in Chip Planner, but cross-probing is much easier. That's why I mentioned timing analyzer because that's the most common way of cross-probing a path into Chip Planner, but you can cross-probe from the RTL Viewer, the Technology Map Viewer, and others. Find the object or path, right-click, and select Locate -> Locate in Chip Planner. The "connectivity schematic" you mention is the resource property viewer/editor, which shows you how specific resources are used in your design (and you can make low-level changes to their use post-fit). When you select a particular resource in the device floorplan (or cross-probe a part of your design to the Chip Planner), this view shows that resource's details. Anything highlighted in blue is part of the resource that is being used by your design. Gray parts are unused.

What you've done here is located an individual resource instead of a path. Again, it's easiest to do what you want from the timing analyzer because you can select a path in a timing report and select Locate *path* in Chip Planner instead of just an individual resource like what you show in your screenshot.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) When you refer to "bird's eye view", do you mean the little picture of the chip where you can click and drag the zoom box to pan around the chip? This is accessed with the toolbar button that looks like a little parrot. As for the Show physical routing command, as mentioned in the guide, this is accessed from the Locate History, which is used typically when you cross-probe from the timing analyzer to look at the physical details of a timing path. What are you wanting to do here?

2) Report Routing Utilization is a heat map view of routing congestion in the device. You can look for hot spots and then correlate with your design through cross-probing. "Fixing" hotspots is trickier because you don't need to fix them unless there is a problem, typically timing issues. Turning off Optimize Hold Timing is a common fix for reducing congestion, but, as the name implies, it can affect your hold timing numbers.

3) Show Physical Routing has been in the tool for ages. It works with all devices in Pro but not all in Standard (some of the older devices are left out, I think). Again, it's only accessible through the Locate History.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @sstrell , thanks for the detailed explanation.

For answering your question:

>> What are you wanting to do here?

Actually, I was a Xilinx User for the past 5 years and would like to switch to Intel FPGA but I'm not so familiar with the capability of Quartus tools compare to Xilinx. Hence, asking such a question.

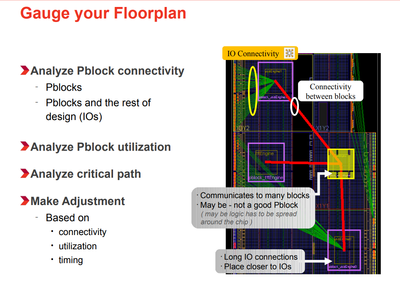

In Xilinx Floorplanner, users can easily gauge the floorplan for the Logic Lock Region connectivity, logic to IO connectivity, and logic to logic connectivity as the screenshot below:

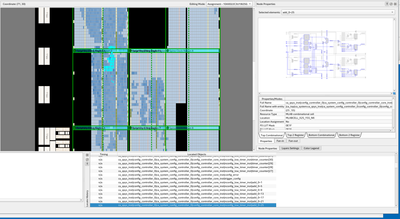

Below is the floorplan view in the Chip Planner:

The connectivity schematic is available on the small window in the Chip Planner, but I don't know how to make the Chip Planner to show the connectivity on floorplan view. Here is my Layers Settings:

The reason to have the connectivity view available in the flooplan is for ease me to have a gauge on how far/close between logic to logic , or logic to IO without get that information from timing report by running Timing Analyzer.

May I know how can I acheive this in the Chip Planner? Thanks in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You have to find and highlight a path. You can search right in Chip Planner, but cross-probing is much easier. That's why I mentioned timing analyzer because that's the most common way of cross-probing a path into Chip Planner, but you can cross-probe from the RTL Viewer, the Technology Map Viewer, and others. Find the object or path, right-click, and select Locate -> Locate in Chip Planner. The "connectivity schematic" you mention is the resource property viewer/editor, which shows you how specific resources are used in your design (and you can make low-level changes to their use post-fit). When you select a particular resource in the device floorplan (or cross-probe a part of your design to the Chip Planner), this view shows that resource's details. Anything highlighted in blue is part of the resource that is being used by your design. Gray parts are unused.

What you've done here is located an individual resource instead of a path. Again, it's easiest to do what you want from the timing analyzer because you can select a path in a timing report and select Locate *path* in Chip Planner instead of just an individual resource like what you show in your screenshot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @sstrell !

Yeah, I did as per your suggestion by cross-probing from a timing path in Timing Analyzer to the Chip Planner, and now I can see the connectivity for that path and it can show the multiple paths connectivity as well.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

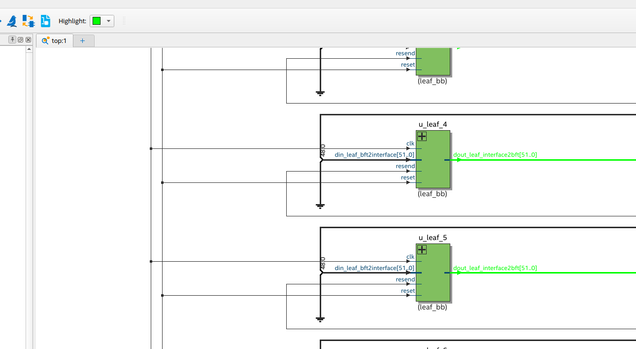

From RTL Viewer, I can select "nodes" and right-click->Locate Node->Locate in Chip Planner.

But when I select nets, there's no option to "Locate". I can highlight(in green) the nets as shown below. But how can I reflect it on Chip Planner?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I did according to your idea by cross-testing from a timing way in Timing Analyzer to the Chip Organizer, and presently I can see the network in that way, and it can show the different ways the web too.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, does the above reply help?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

As your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page