- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

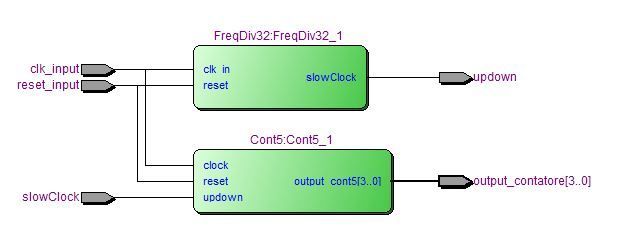

I am a beginner user of Quartus Prime Lite software (I have to do a project for my University) and I am trying to use the output o a component as the input of the other component... but I cannot do it... I looked for it in the Internet but I do not know whats wrong in my code.

I attach the image of the module I created, the output value "slowclock" or freqDiv32 has to be the input for "updown" in Cont5.

I hope I explained clearly the issue, it is probably a very easy thing but I need some help, please.

Grazie,

Margherita from Italy

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Welcome to the forum.

Can you share an archive (use in quartus the option project / archive) with us ?

We might be better able to help you if you do.

Best Regards,

Johi.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

sure, I saved the .qar file

I attach it at this answer.

Grazie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I forgot to mention that I added a possible solution to your problem in the previous post.

Best Regards,

Johi.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello there ,

In the top module (progetto.vhd), you can use the signal to connect the ports in the component instantiation. Also if you want the port out in the top module ,you can connect the top port to same signal. Then synthesis tool infer the signal using buffer.

I attached modified top module ( progetto.vhd) and synthesized schematic block diagram for your reference.

In case if you dont want to instantiate both the slowdown/updown port , you can comment below two lines in top module.

slowClock <= updown_slowclk_sig;

updown <= updown_slowclk_sig;

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

thank you to both of you for your answers!

Now I have undesrtood what you did.

Thank you for the help,

Margherita

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page