- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

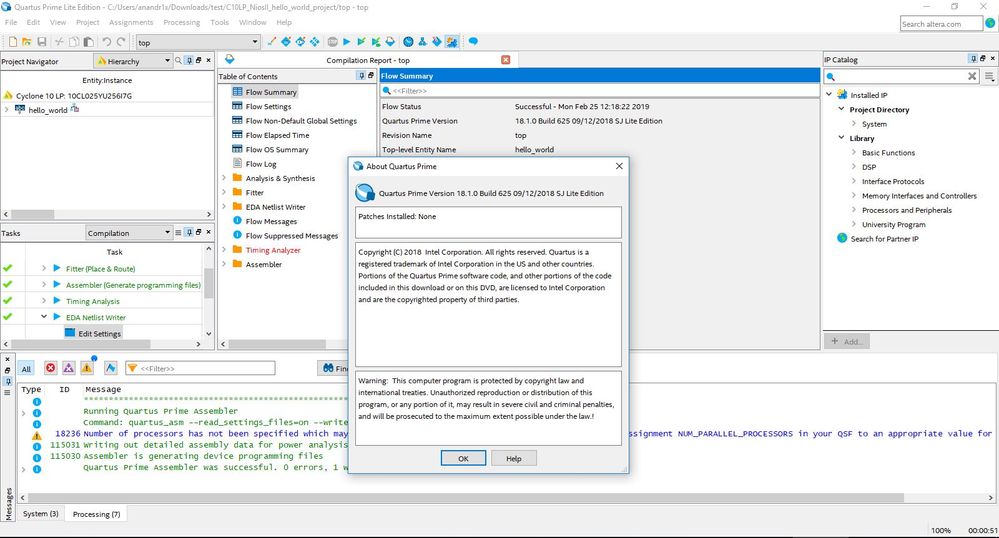

"hello world" examples fails on EDA Netlist Writer stage with Unconstrained error on SYS_CLK50M field.

"reference design" - philosophers example compiles wihtout doing EDA stage.

Link Copied

2 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have used Cyclone 10 LP Nios II 'Hello World' Design which work fine without any error.(opened .par ->upgrade -> start compilation)

Try again downloading the example or create your own design by referring to below link.

https://fpgawiki.intel.com/uploads/2/2d/C10LP_Nios_II_Hello_World_Lab_Manual.pdf

Can you share image of you EDA netlist setting or your project itself.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anana,

thanks for ur reply to the query re Nios2 problem. I got it working ok

and am enjoying playing around with the system a bit. The problem I had

I thinks stems from the documentation being a bit out of date. The pdf

guide from the design store talked about compiling the nios2 core from a

qsr source whereas all you have to do is add the qip file to your

project and compile. I traced the compile problem in EDA to a message

like "functional simulation is the only simulation available for the

device type but is turned off".

I turned it on at settings -> EDA -> More EDA Netlist Writer Settings ->

Generate functional simulation netlist, and compilation was successful.

That was before I added the qip file, hence I dont know if it was

necessary, but it was still turned on when I compiled with the qip file

added without problems.

Thanks again for ur response

P.S. Do u know of any documentation for the JTAG UART interface that

lets you interact with the board from ur own programs without using the

nios2-terminal program. I can always redirect the stdin, stdout of

nios2-terminal which is probably easier anyway.

P.P.S. I was using quartus 18.1 Lite on Linux.

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page