- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There's a problem that makes us confus.

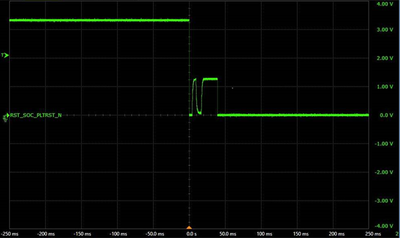

The input reset signal is like this

The unstable part would stay about 40 ms long.

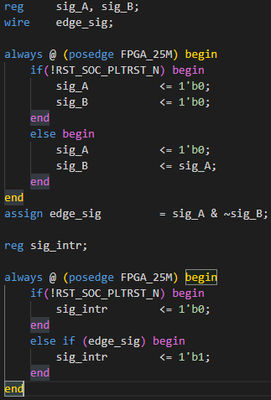

Here's our source code for trigger

Here's the waveform in SignalTap

When sig_A & sig_B is all 0

edge_sig should be 0

But sig_intr appear a pulse when doing reset

Will this situation because of the unstable of reset?

BTW, we also disscuss about the possiblitiy of synchonus reset woule influence sig_intr problem,

but we are not sure if this would be the problem after synthesis or not.

Thanks.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It certainly could be because of the unstable pulse. Signal Tap can't help with capturing an issue like that. Check your timing analysis. What does your .sdc look like?

But stranger is that there is no way in your design for sig_A to ever go high. Typo in your reset process?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your replay.

In our design, there's only have clock in .sdc file

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Regards

Frank

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your replay.

The source of reset is from the other CHIP outside FPGA.

We guess the unstable waveform might be caused by PCB layout.

We tried to synchronus reset using shift register

Then replace original procedure reset part by higher bit of shift register

So far, the test result seem fine.

But we think the best way to solve this problem is to figure out the unstable problem of reset.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Higher bit shift register might be a good temporary workaround. But you still need to root cause from outside for unstable pulse. Afraid might cause another issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution, give Kudos and rate 5/5 survey

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page