- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Support and Expert,

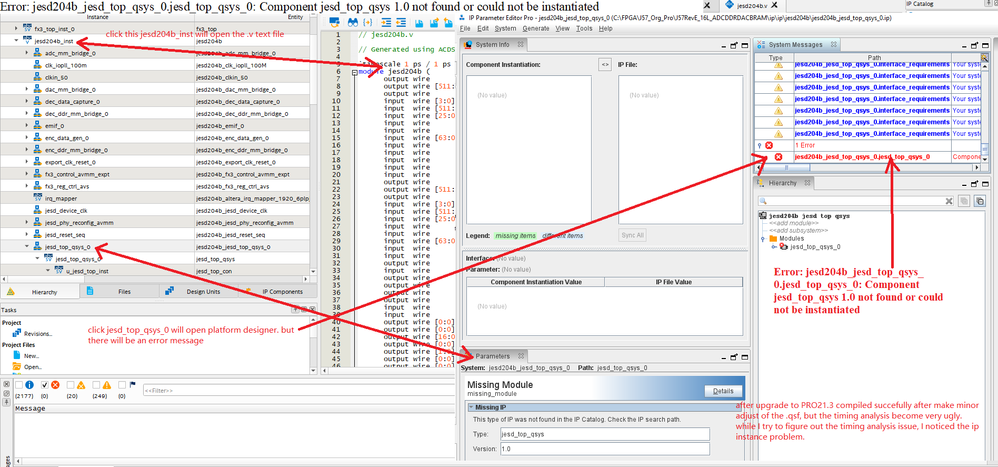

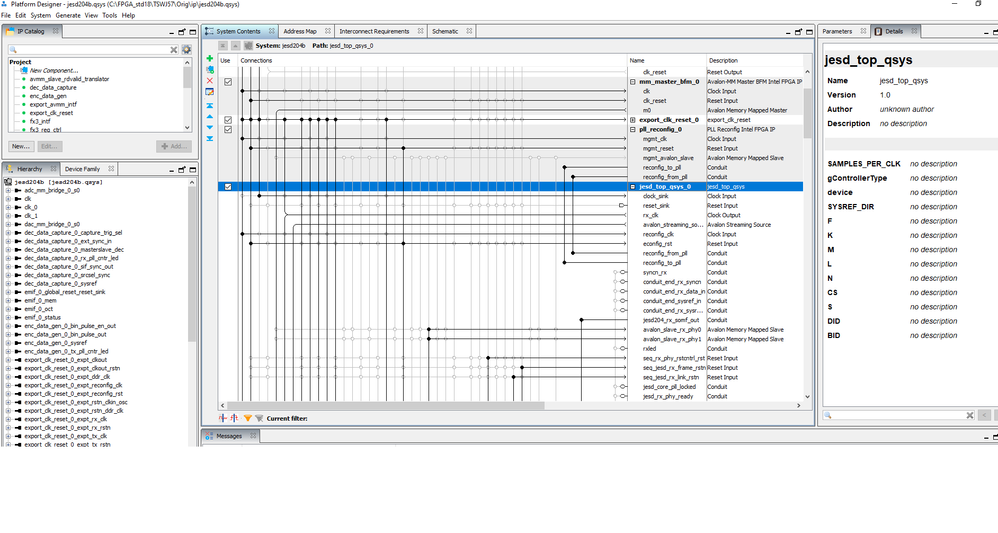

I have a project from TI, it is a Jesd204B design. the original design was in old Quartus standard edition. may be 16 or 17, first I updated to 18.1. everything seems working. there may be only 1 or 2 path over the timing constrains. but overall looks pretty good. after I bought an Intel Arria 10 dev kits. I got a Quartus Pro license, so I try to upgrade to Pro 21.3. after some minor modification in qsf file. the compilation can complete successfully, but there are thousands of timing failure. while I tracing this problem, I opened one IP/qsys called jesd_top_qsys_0, PlatformDesigner report an error message. I quoted here "Error: jesd204b_jesd_top_qsys_0.jesd_top_qsys_0: Component jesd_top_qsys 1.0 not found or could not be instantiated.

I don't understand what this means, because the project can go though all the compilation without any error message. why when I open one module in the project it report errors.

please give me some suggestion, appreciate your help.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sun,

I believe delete and re-add the IP is the best way to try and not complicated as you thought (drag and connect). Make sure you have a back up qar before make any changes. My suggestion if you are not sure what parameter, open the original design in STD, mark what parameters necessary and add them in new added IP in PRO. Then generate and compile. This should be able to fix your issue.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

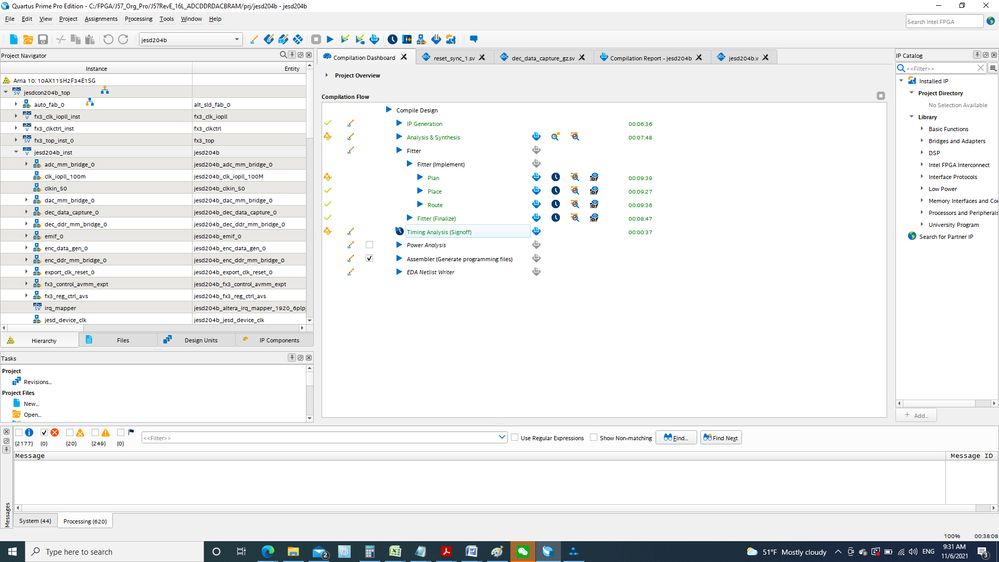

here is the image of the compilation complete image

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You probably need to delete and re-add the IP in your Platform Designer system. The tool may not have been able to update the old version.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sstrell,

Thank you for the reply, I am new to this platform designer, still not that confident to replace the IPs. but if it is the right way to fix the problem, I will give it a try. appreciate your help.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

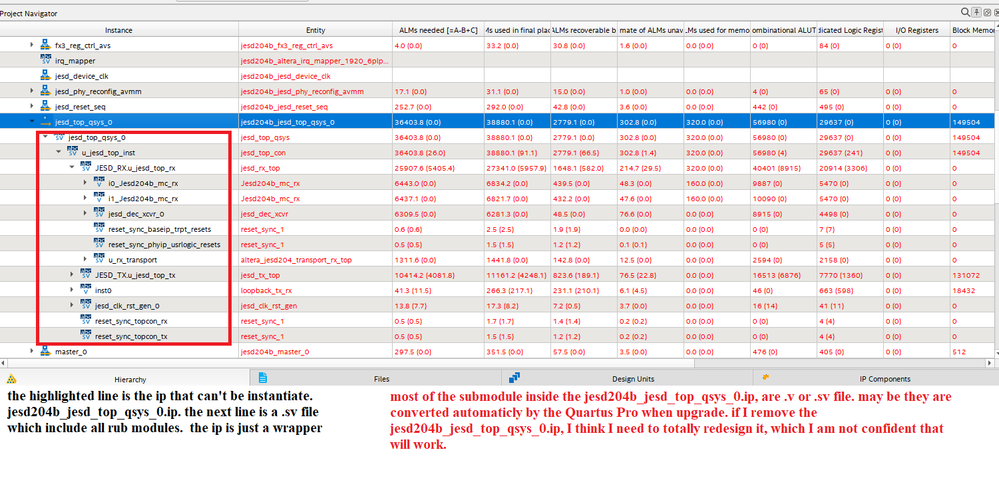

Hi Sstrell

I had a look regenerating the IPs, it is much more complicate than I thought, it seems to me like redesign everything, here is why. if I understand correctly, in the following picture, the blue color highlighted line is the IP, it is just a wrapper layer. you can see all the parameters are exactly same to the module under it, which is a .SV file. I am still working on the timing understanding and fixing. I just want to know does my understanding here make any sense.

thank you for your help.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sun,

I believe delete and re-add the IP is the best way to try and not complicated as you thought (drag and connect). Make sure you have a back up qar before make any changes. My suggestion if you are not sure what parameter, open the original design in STD, mark what parameters necessary and add them in new added IP in PRO. Then generate and compile. This should be able to fix your issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SyafieqS,

I 100% believe and I am going to follow. I am relative new to the Pro and Platform Designer. I need get familiar with the design platform as much as I could, then I start to delete and update. there are two variables, one is that the original design is on 10AX115H2F34E1SG.

I need port it to the Intel Arria 10 GX dev board. it is a 10AX115S2F45E1SG. one is the Quartus will be upgrade to Pro. any mistake in this two stage will make me loss the track.

with the help Adzim, I can compile the design use Pro. once I make progress on the time analysis. I will start to regenerate everything.

Thank you very much for the support.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SyafieqS,

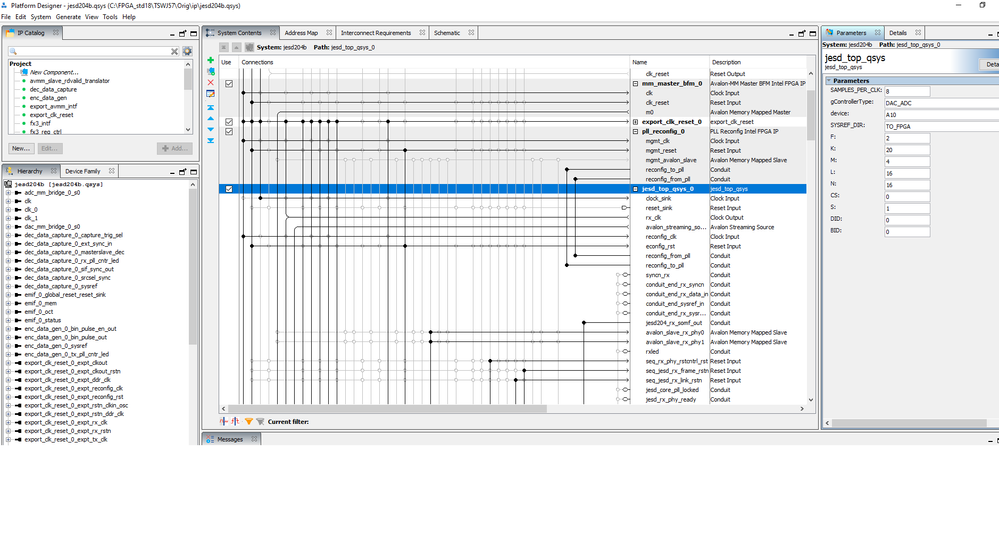

I accepted your post as solution, that is from the strategy level, now when I start the operation. the first problem I have is shown in the following screen capture.

jest_top_qsys_0 here is a submodule of jest204b, from parameter you can see the LMF is 16, 4, 2. when I create a new jest_top. the Maximum L value is 8. the problem is that I couldn't find the jest_top_qsys_0.qsys in the project. from the detail screen capture, the author is unknown, and all description are none. I hope I can have a little bit more detail besides the strategy in this special case.

there is only one sub-directory called synth in directory

C:\FPGA_std18\TSWJ57\Orig\ip\jesd204b\jesd_top_qsys_10

almost all files in synth are .sv file.

seems I need re-generate a new .qys called jesd_top_qsys_10, but I lost the track of this module, even the project compile successfully.

Appreciate your help.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Sun,

I believe all the files .sv mentioned is the necessary files for your sub-module of jesd_top_qsys_10. In that folder you mentioned, there should be a jesd_top_qsys_10.sv which you can use that as top file instead of qsys. Just need to include all that files in the project.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page